# **NOTICE**

Information furnished by Rockwell International Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Rockwell International for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Rockwell International other than for circuitry embodied in Rockwell products. Rockwell International reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

MONOFAX is a registered trademark of Rockwell International.

# **Table of Contents**

| 1. INTRODUCTION                                | 1-1  |

|------------------------------------------------|------|

| 1.1 FACSIMILE MODEM                            | 1-1  |

| 1.2 VOICE AND AUDIO CODECS (-V OPTION)         | 1-1  |

| 1.3 SPEAKERPHONE (-S OPTION)                   | 1-1  |

| 1.4 AUTOMATIC SPEECH RECOGNITION (-R OPTION)   |      |

| 1.5 V.23 FULL-DUPLEX MODEM AND CALLER ID       |      |

| 1.6 FEATURES                                   |      |

|                                                |      |

| 1.7 TECHNICAL SPECIFICATIONS                   |      |

| 1.7.1 Modem                                    |      |

| 1.7.3 Voice Codec Mode (-V Option)             |      |

| 1.7.4 ADPCM Audio Codec Mode (-V Option)       |      |

| 1.7.5 PCM Audio Codec Mode                     |      |

| 1.7.6 Speakerphone Mode (-S Option)            |      |

| 1.7.7 Automatic Speech Recognition (-R Option) |      |

| 1.7.8 Room Monitor Mode                        | 1-8  |

| 2. HARDWARE INTERFACE SIGNALS                  | 2-1  |

| 3. SOFTWARE INTERFACE                          | 3-1  |

| 3.1 INTERFACE MEMORY                           | 3-1  |

| 3.1.1 Interface Memory Map                     | 3-1  |

| 3.1.2 Interface Memory Bit Definitions         |      |

| 3.2 SOFTWARE INTERFACE CONSIDERATIONS          | 3-19 |

| 3.2.1 Parallel Data Transfer                   |      |

| 3.2.2 Programmable Interrupt Feature           |      |

| 3.2.3 8-Bit PCM Audio Codec Mode Operation     |      |

| 3.2.4 16-Bit PCM Audio Codec Mode Operation    |      |

| 3.2.5 DTMF Receiver                            |      |

| 3.2.6 V.21 Channel 2 FSK 7E Flag Detector      |      |

| 3.2.8 Caller ID Mode Operation                 |      |

| 3.2.9 High Speed Timing                        |      |

| 3.2.10 Power-On/Reset DSP Test Mode            |      |

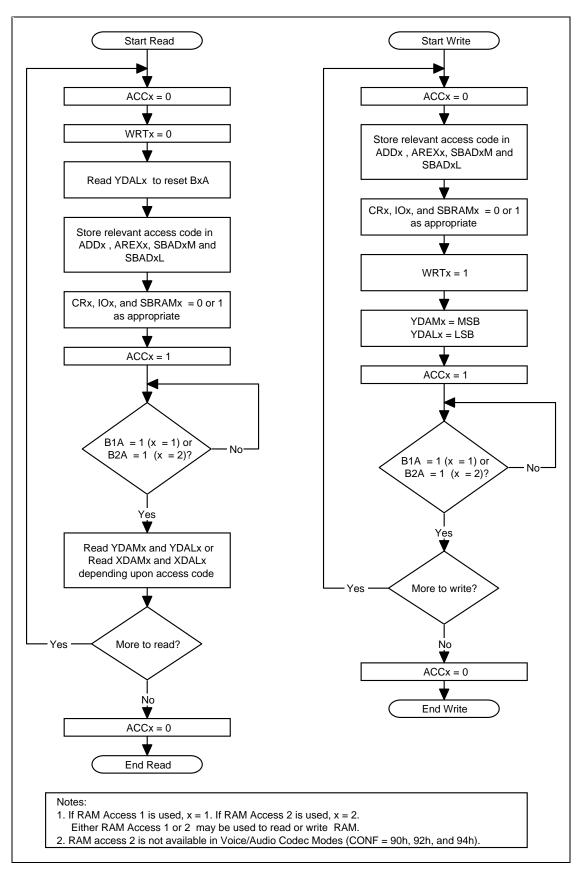

| 4. DSP RAM ACCESS                              | 4-1  |

| 4.1 INTERFACE MEMORY ACCESS TO DSP RAM         | 4-′  |

| 4.1.1 Host Programmable Data                   |      |

| 4.1.2 Host DSP RAM Read And Write Procedures   |      |

| 4.1.3 DSP RAM Read Procedure                   |      |

| 4.1.4 DSP RAM Write Procedure                  |      |

| 4.2 DIAGNOSTIC DATA SCALING                    |      |

| 4.3 INTEGRATED ANALOG CONTROL REGISTERS        |      |

| 4.3.1 IACR1 IA Control Register 1              |      |

| 4.3.2 IACR2 IA Control Register 2              |      |

| 4.3.3 IACR3 IA Control Register 3              | 4-Z3 |

| 5. HDLC FRAMING                                                       | 5-1  |

|-----------------------------------------------------------------------|------|

| 5.1 HDLC FRAMES                                                       | 5-1  |

| 5.1.1 Frame Fields                                                    | 5-1  |

| 5.1.2 Flags                                                           |      |

| 5.1.3 Address Field                                                   |      |

| 5.1.4 Control Field                                                   |      |

| 5.1.5 Information Field                                               |      |

| 5.1.6 Zero Insertion                                                  |      |

| 5.1.8 Frame Check Sequence (FCS)                                      |      |

| 5.1.9 Frame Abortion, Frame Idle, And Time Fill                       |      |

| 5.2 IMPLEMENTATION                                                    | 5-3  |

| 5.2.1 Mode Selection                                                  | 5-5  |

| 5.2.2 Transmission and Reception Rate                                 |      |

| 5.2.3 Transmitter and Receiver Initialization                         |      |

| 5.2.4 Flag Transmission and Reception                                 |      |

| 5.2.5 Information Field Transmission and Reception                    |      |

| 5.2.6 FCS and Ending Flag Transmission and Reception                  |      |

| 5.2.8 Underrun and Overrun Conditions                                 |      |

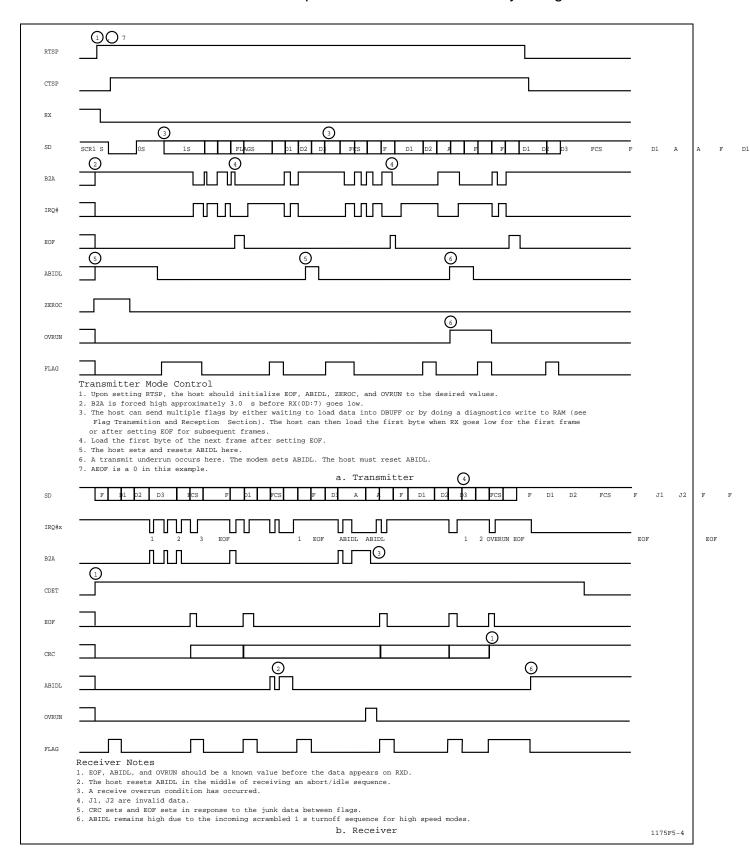

| 5.2.9 Transmit Mode Control                                           |      |

| 5.3 EXAMPLE APPLICATION                                               |      |

| 5.3.1 Transmitter Example                                             | 5-9  |

| 5.3.2 Receiver Example                                                | 5-9  |

| 6. TONE DETECTOR FILTER TUNING                                        | 6-1  |

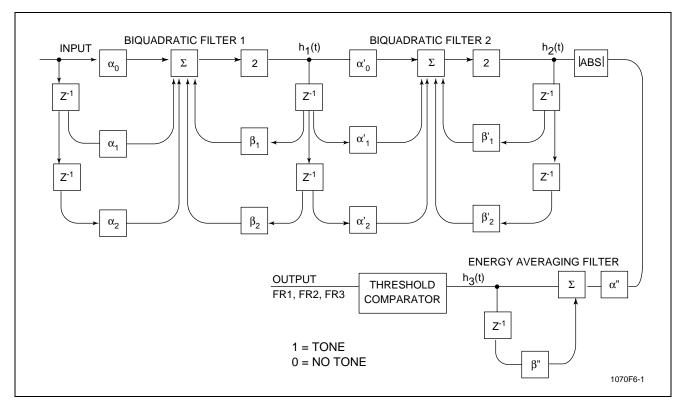

| 6.1 PROGRAMMABLE TONE DETECTORS                                       | 6-1  |

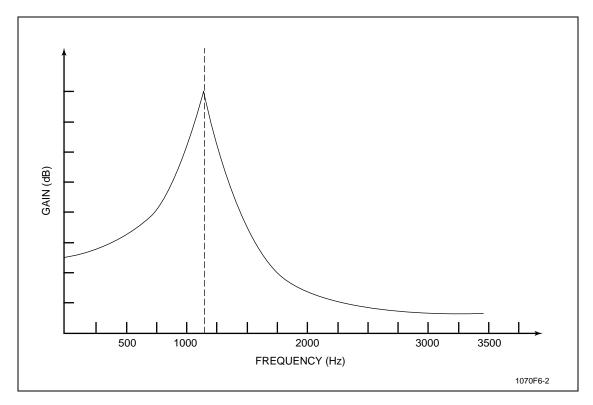

| 6.1.1 Computation of Tone Detector Coefficients                       | 6-1  |

| 6.1.2 Energy Averaging Filter                                         |      |

| 6.1.3 Filter Coefficients                                             |      |

| 6.2 TONE DETECTORS IN VOICE CODEC, AUDIO CODEC AND SPEAKERPHONE MODES | 6-7  |

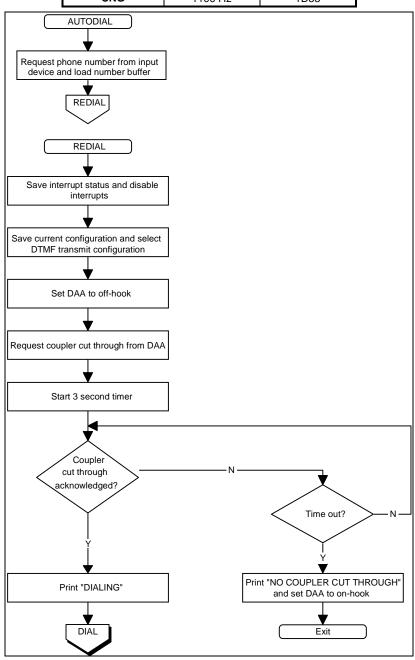

| 7. DTMF DIALING WITH AUTO DIALER                                      | 7-1  |

| 7.1 DTMF REQUIREMENTS                                                 | 7-1  |

| 7.2 SETTING OSCILLATOR PARAMETERS                                     | 7-2  |

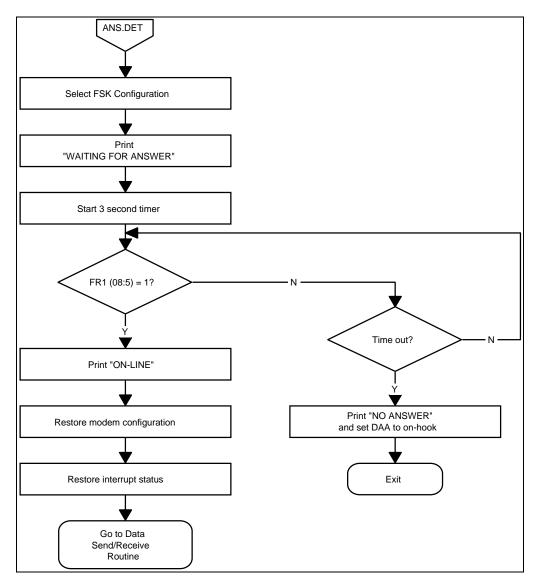

| 7.3 DETECTING ANSWER TONE                                             | 7-2  |

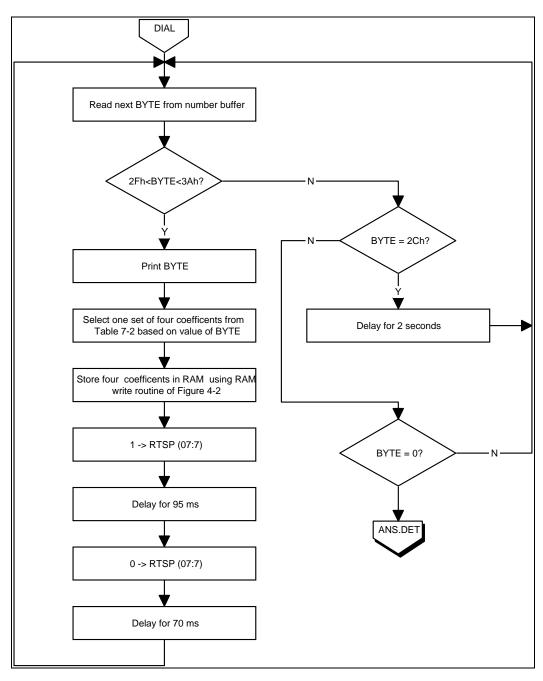

| 7.4 COMPLETE CALLING SEQUENCE                                         | 7-2  |

| 7.5 SINGLE TONE GENERATION                                            | 7-5  |

| 8. VOICE CODEC AND ADPCM AUDIO CODEC MODES WITH ROOM MONITOR          | 8-1  |

| 8.1 VOICE CODER AND ADPCM AUDIO CODER                                 | 8-1  |

| 8.1.1 Voice and Audio Activated Message Encoding                      | 8-3  |

| 8.1.2 End of Message Detection                                        | 8-3  |

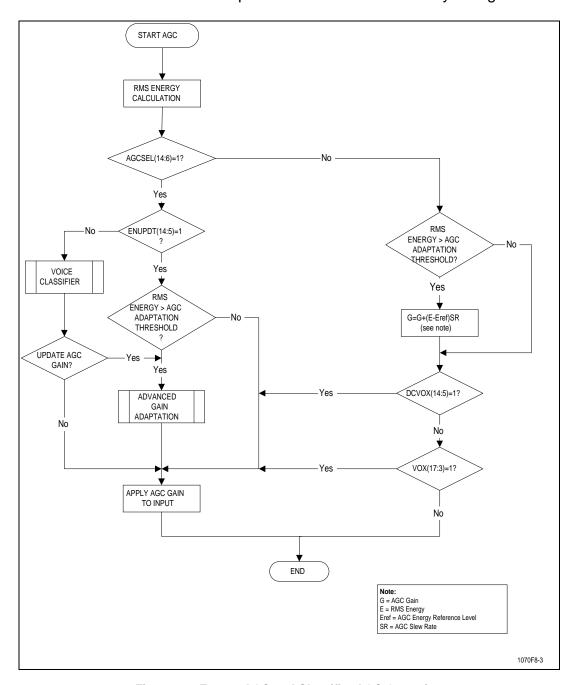

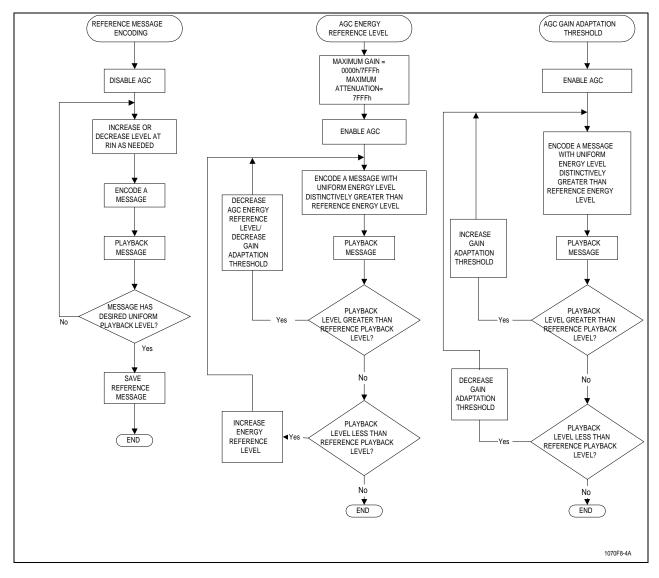

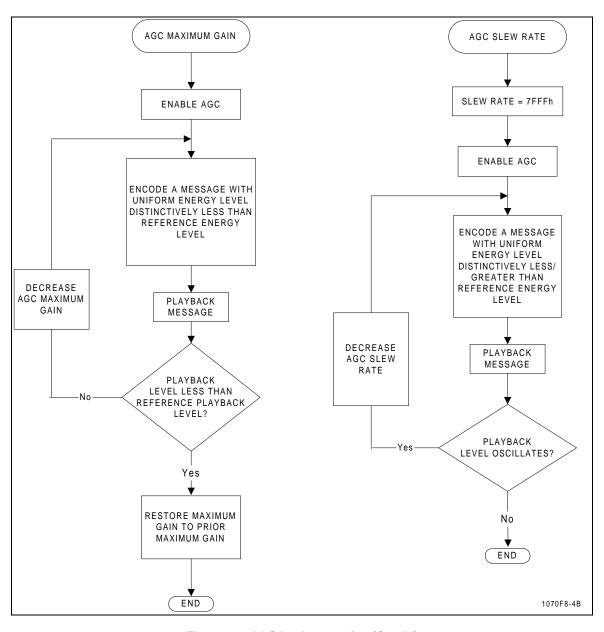

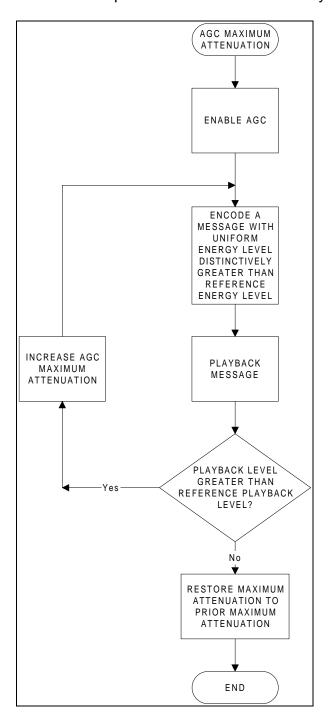

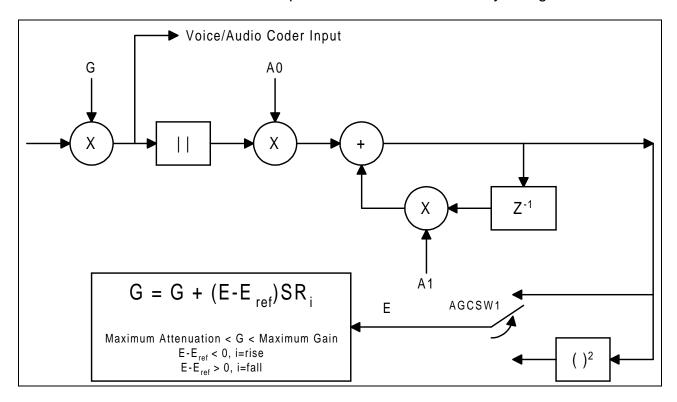

| 8.1.3 Coder Automatic Gain Control (AGC)                              |      |

| 8.1.4 Sample Rate VOX                                                 |      |

| 8.2 VOICE DECODER AND ADPCM AUDIO DECODER                             |      |

| 8.2.1 Prevent False ICM DTMF Detection of OGM DTMF                    |      |

| 8.2.2 Decoder Skip Forward/Backward During Message Playback           |      |

| 8.3 ERROR CORRECTION CODING AND ARAM MESSAGE STORAGE                  |      |

| 8.4 ROOM MONITOR                                                      | 8-16 |

| 8.5 TONE, DTMF, AND TYPE II CALLER ID CAS DETECTION                   | 8-17 |

| 8.6 CODER BIQUAD PRE-FILTER AND DECODER BIQUAD POST-FILTER            | 8-17 |

| 8.6.1 Filter Equations                        | 8-17 |

|-----------------------------------------------|------|

| 8.6.2 Coder TX Biquad Pre-Filter              | 8-18 |

| 8.6.3 Decoder RX Biquad Post-Filter           | 8-19 |

| 8.6.4 Default Parameters                      | 8-19 |

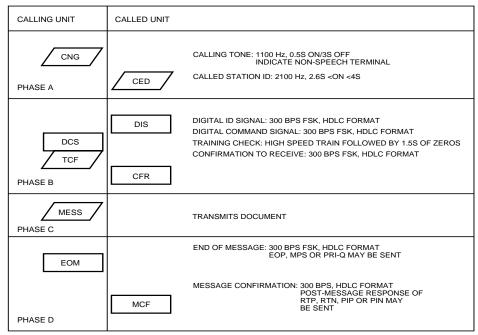

| 9. T.30 IMPLEMENTATION                        | 9-1  |

| 9.1 GENERAL                                   | 0.4  |

| 9.1 GENERAL<br>9.1.1 Phase A                  |      |

| 9.1.1 Phase A                                 |      |

| 9.1.3 Phase C                                 |      |

| 9.1.4 Phase D                                 |      |

| 9.1.5 Phase E                                 |      |

| 9.1.6 Flowcharts                              |      |

| 9.2 ERROR CORRECTION MODE                     | 9-24 |

| 9.2.1 General                                 |      |

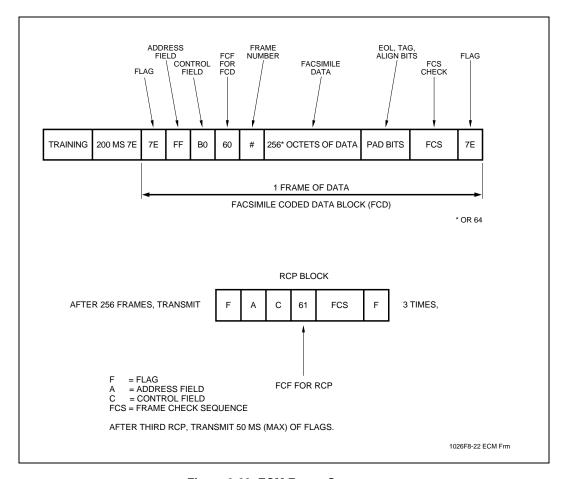

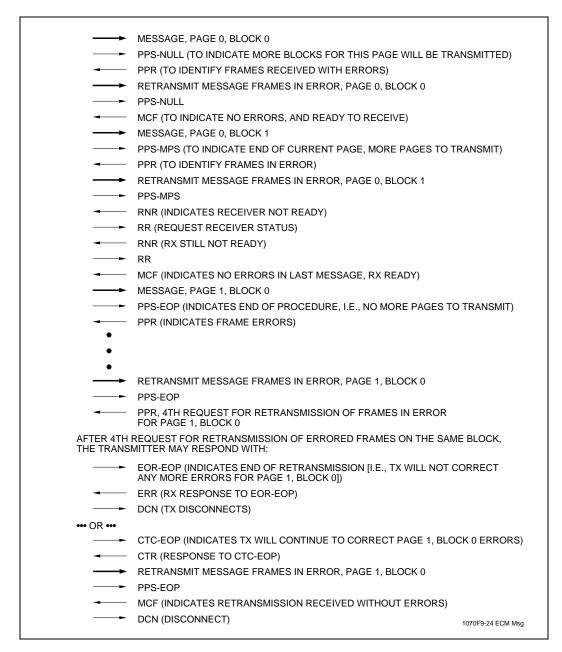

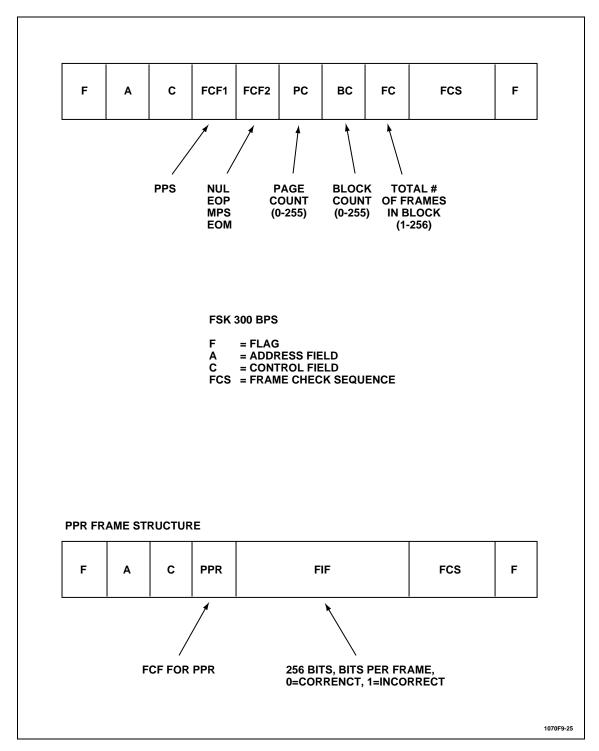

| 9.2.2 ECM Frame Structure                     | 9-24 |

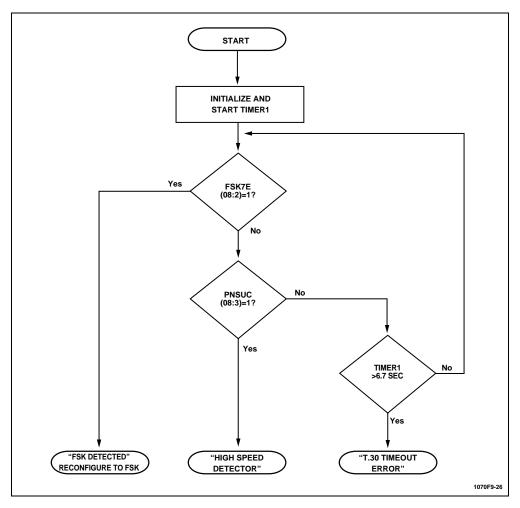

| 9.3 SIGNAL RECOGNITION ALGORITHM              | 9-28 |

| 9.3.1 FSK vs. High Speed                      |      |

| 9.3.2 FAX vs. Voice                           | 9-28 |

| 9.4 SHORT TRAIN EXAMPLE                       | 9-32 |

| 10. CALLER ID                                 | 10-1 |

| 10.1 INTRODUCTION                             | 10-1 |

| 10.2 CALLING NUMBER DELIVERY SPECIFICATION    |      |

| 10.3 PARAMETERS                               |      |

|                                               |      |

| 10.4 PROTOCOL                                 |      |

| 10.4.1 Channel Seizure Signal                 |      |

| 10.4.3 Message Type Word                      |      |

| 10.4.4 Message Length Word                    |      |

| 10.4.5 Data Words                             |      |

| 10.4.6 Checksum Word                          |      |

| 10.4.7 Example CND Single Data Message        |      |

| 10.5 DAA REQUIREMENTS                         |      |

| 10.6 MODEM REQUIREMENTS                       | 10-3 |

| 10.7 APPLICATIONS                             | 10-3 |

| 10.8 REFERENCES                               | 10-3 |

| 10.9 TYPE II CALLER ID                        | 10-3 |

| 11. DIGITAL EQUALIZATION/HIGH PASS FILTER     | 11-1 |

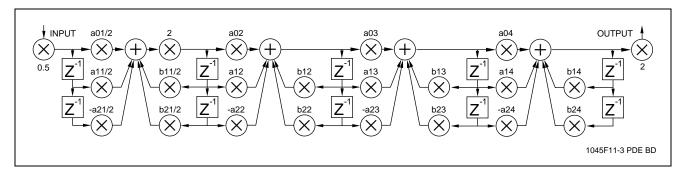

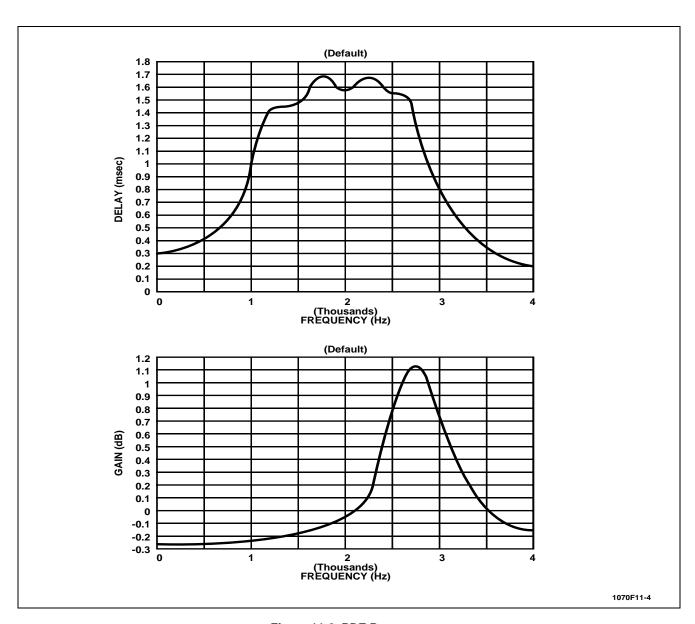

| 11.1 PROGRAMMABLE DIGITAL EQUALIZER (PDE)     | 11 1 |

| 11.1.1 PDE Frequency Response                 |      |

| 11.1.2 PDE Coefficients                       |      |

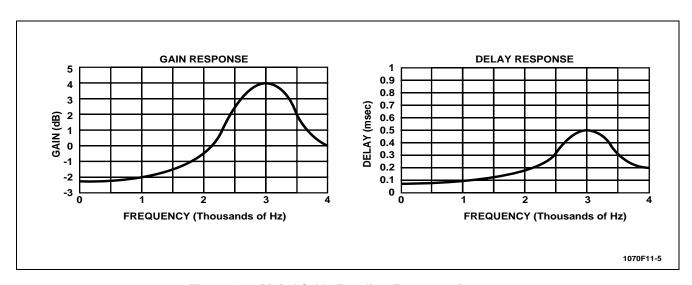

| 11.2 FIXED DIGITAL CABLE COMPROMISE EQUALIZER |      |

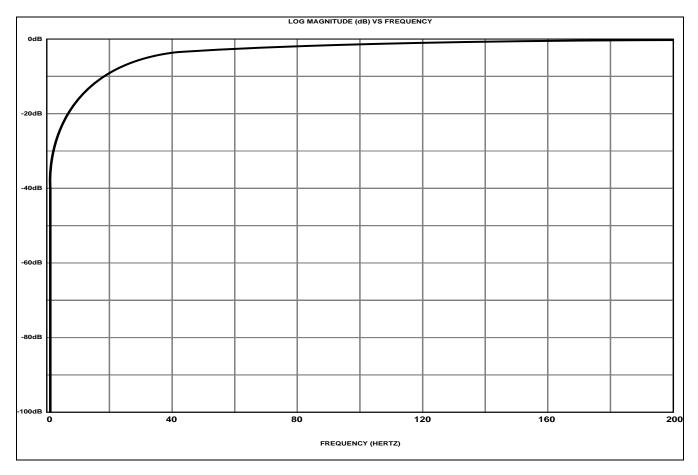

| 11.3 HIGH PASS FILTER                         | 11-1 |

| LLA DIGO PASS EILLEK                          | 11-1 |

| 2. SPEAKERPHONE                                       |       |

|-------------------------------------------------------|-------|

| 12.1 INTRODUCTION                                     | 12-2  |

| 12.2 SPEAKERPHONE RAM ACCESS                          | 12-3  |

| 12.3 SPEAKERPHONE DESIGN ISSUES                       | 12-9  |

| 12.3.1 Microphone/Speaker Placements                  | 12-9  |

| 12.3.2 Microphone and Speaker Gains                   |       |

| 12.3.3 Hybrid Interface                               |       |

| 12.4 SPEAKERPHONE MODES                               | 12-10 |

| 12.4.1 FDX Speakerphone Mode                          | 12-10 |

| 12.4.2 Half Duplex Speakerphone Mode                  |       |

| 12.4.3 FDX and HDX Intercom Support Modes             |       |

| 12.4.4 Tone Transmit Mode                             |       |

| 12.4.6 Speakerphone Modes and Active Bits             |       |

| 12.5 SPEAKERPHONE CONTROL                             |       |

| 12.5.1 Speakerphone Interface Control Registers       |       |

| 12.5.2 Biguad Filters                                 |       |

| 12.5.3 Microphone Volume Control                      |       |

| 12.5.4 Line Volume Control                            |       |

| 12.5.5 Speaker Volume Control                         |       |

| 12.5.6 Microphone and Speaker Muting                  |       |

| 12.5.7 Microphone and Speaker AGC                     |       |

| 12.5.9 Scaling of Transmit Output to Line             |       |

| 12.5.10 Scaling of Receive Input to Speaker           |       |

| 12.6 CONVERSATION RECORDING AND MESSAGE PLAYBACK      |       |

| 12.7 TONE, DTMF, AND TYPE II CALLER ID CAS DETECTION  | 12-18 |

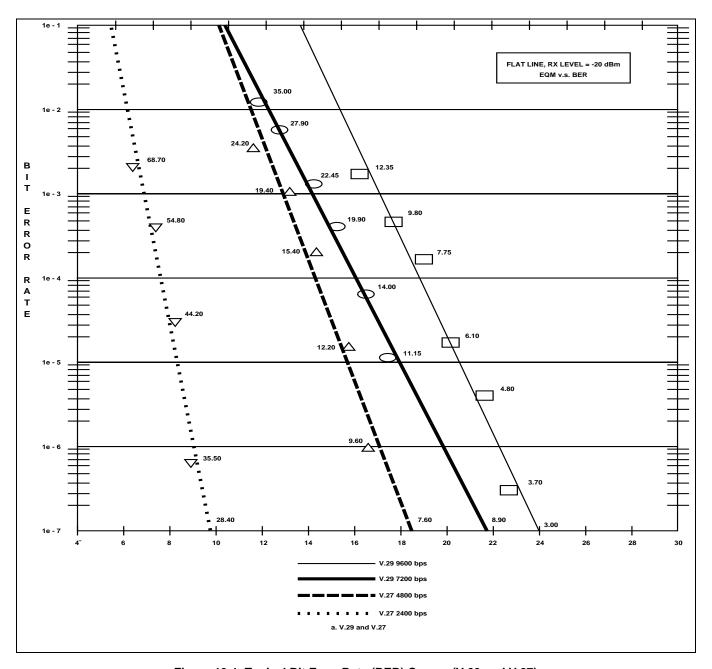

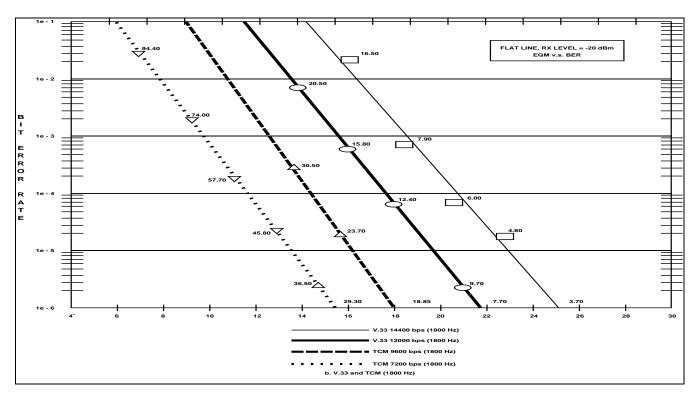

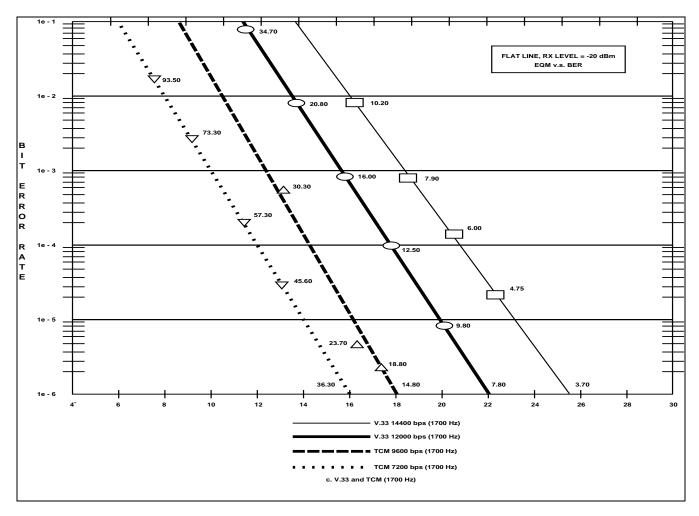

| 13. PERFORMANCE                                       | 13-1  |

| 13.1 TYPICAL BIT ERROR RATES                          | 13-1  |

| 13.2 TYPICAL PHASE JITTER                             | 13-1  |

| 13.3 DTMF PERFORMANCE                                 | 13-1  |

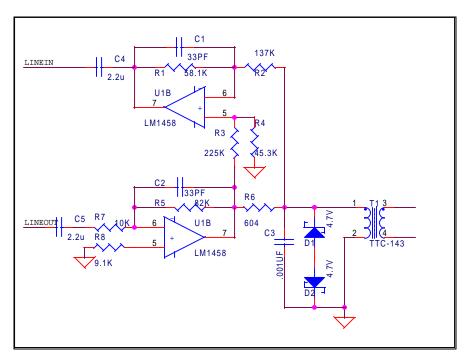

| 14. MODEM INTERFACE CIRCUIT                           | 14-1  |

| 14.1 CIRCUIT AND COMPONENTS                           | 14-1  |

| 14.1.1 Crystal/Oscillator Specifications              |       |

| 14.1.2 Transmit Level and Receive Threshold Trimmers  |       |

| 14.1.3 Echo Canceller Working Condition               |       |

| 14.1.4 Room Acoustic Ecno Canceller Working Condition |       |

| 14.2.1 General Board Layout Guidelines                |       |

| 14.2.1 General Board Layout Guidelines                |       |

| 14.2.3 Crystal Oscillator EMI Considerations          |       |

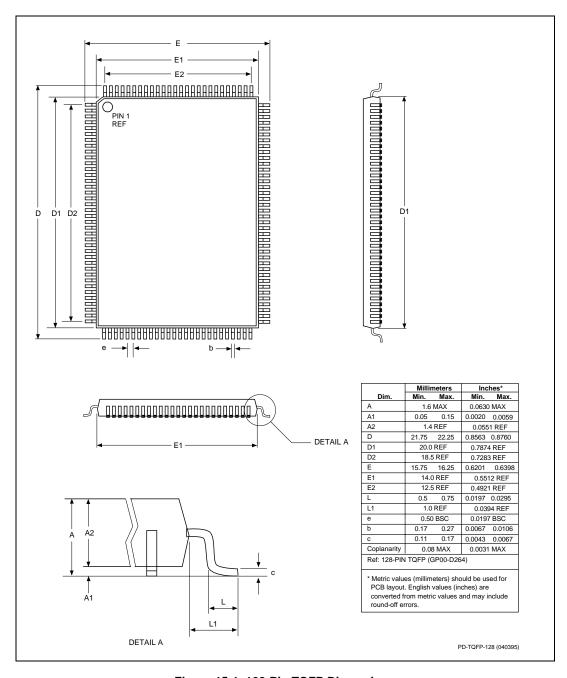

| 15 PACKAGE DIMENSIONS                                 | 15-1  |

# **List of Figures**

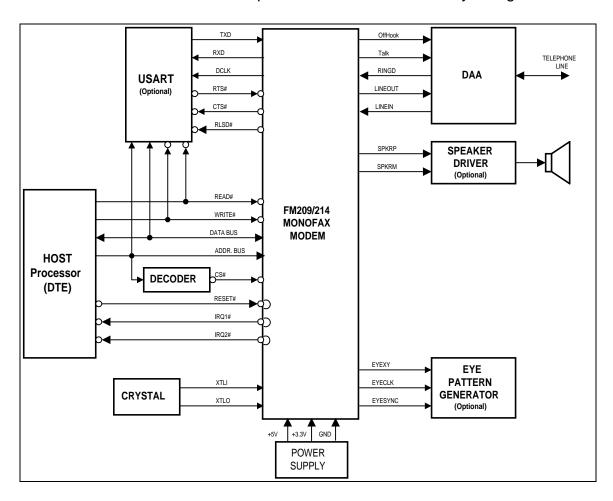

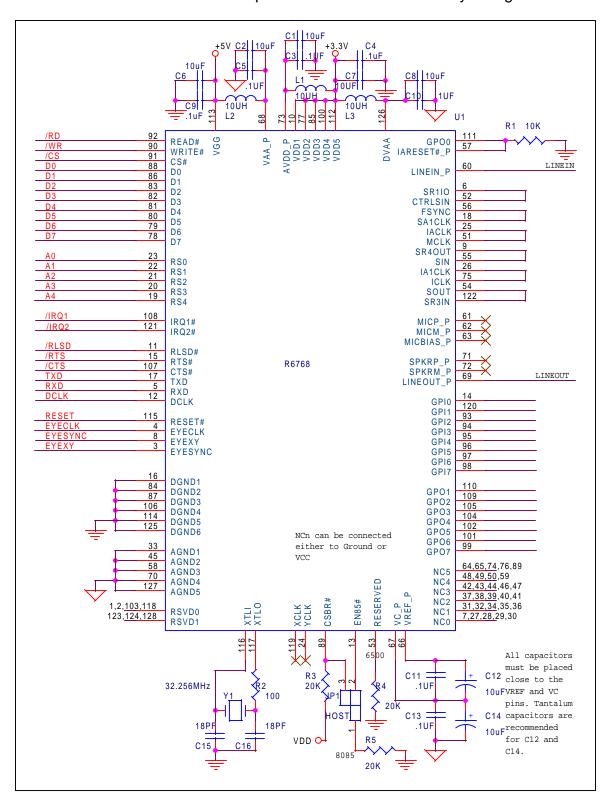

| Figure 2-1. Modem Functional Interconnect Diagram (Fax)                         | 2-2  |

|---------------------------------------------------------------------------------|------|

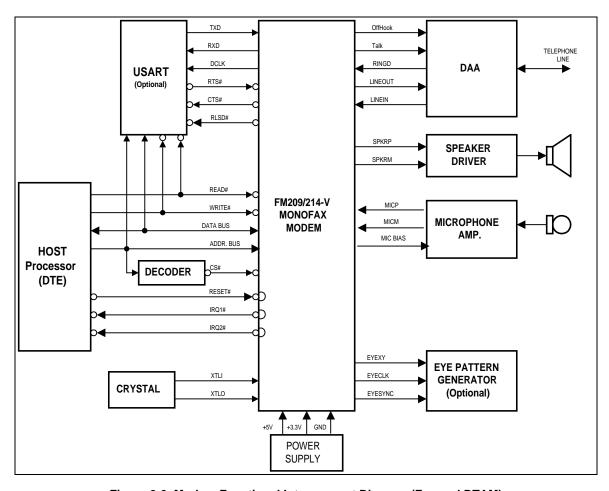

| Figure 2-2. Modem Functional Interconnect Diagram (Fax and DTAM)                | 2-3  |

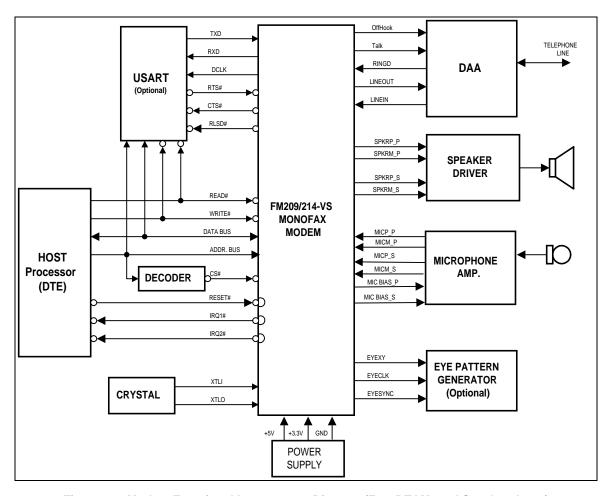

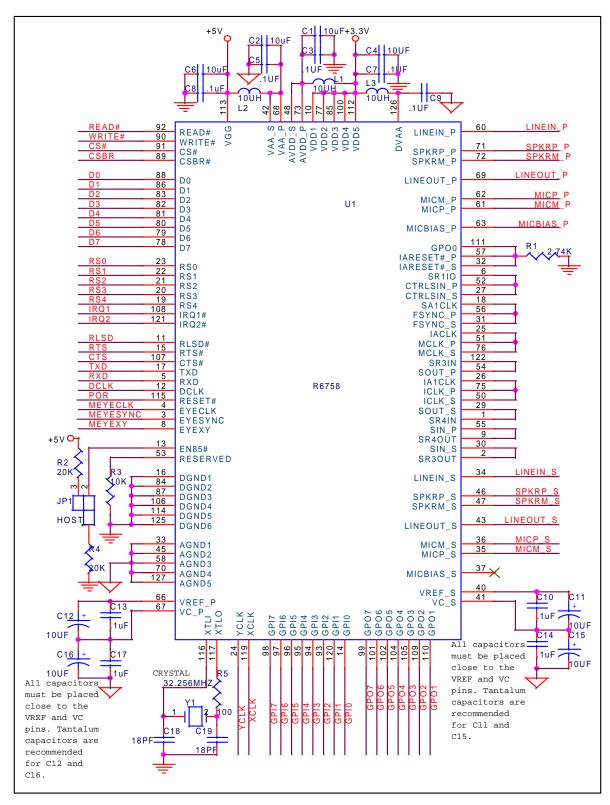

| Figure 2-3. Modem Functional Interconnect Diagram (Fax, DTAM, and Speakerphone) | 2-4  |

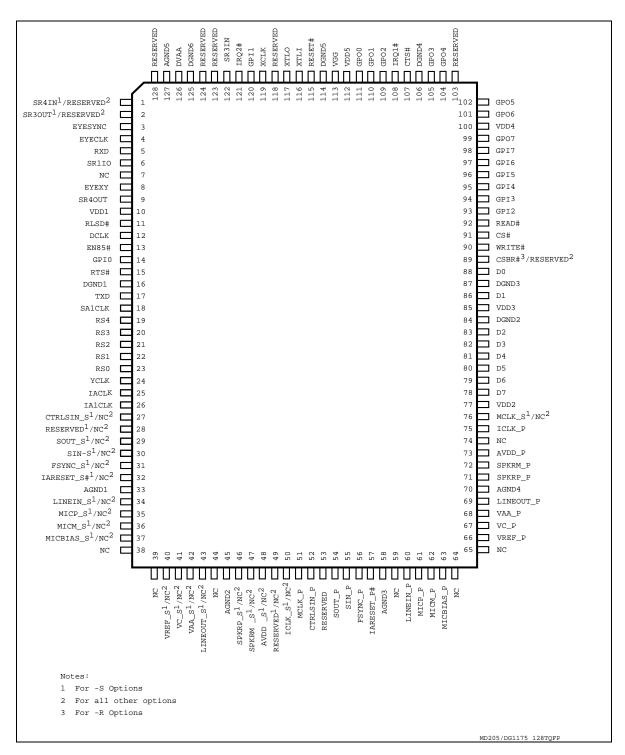

| Figure 2-4. Modem Pin Signals - 128-Pin TQFP                                    | 2-5  |

| Figure 2-2. Microprocessor Interface Waveforms                                  | 2-16 |

| Figure 2-3. Transmitter Signal Timing                                           | 2-17 |

| Figure 2-4. Receiver Signal Timing                                              | 2-18 |

| Figure 2-5. Eye Pattern Timing                                                  | 2-18 |

| Figure 2-6. Eye Pattern Circuit                                                 | 2-19 |

| Figure 3-1. Interface Memory Map                                                | 3-2  |

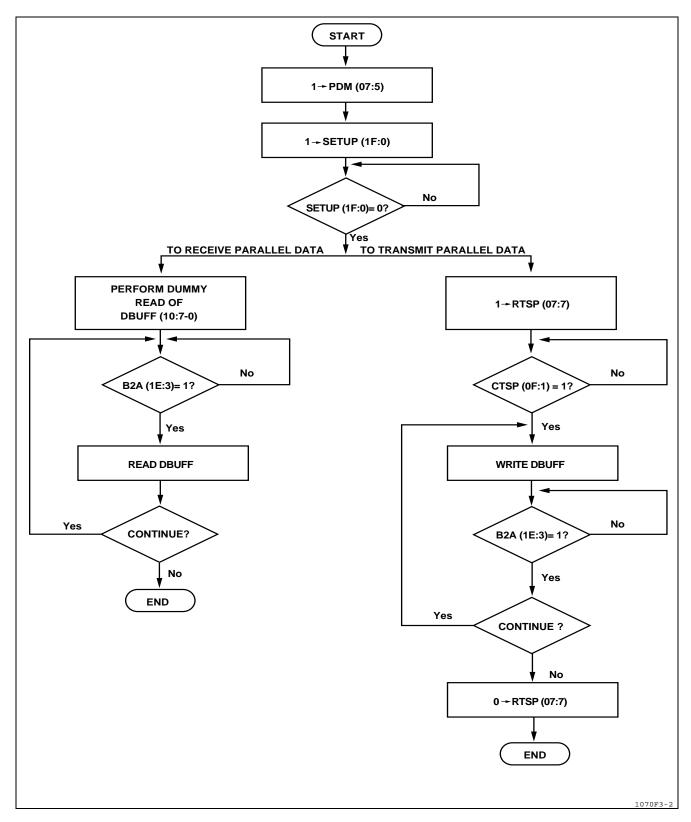

| Figure 3-2. Parallel Data Transfer Routine                                      | 3-20 |

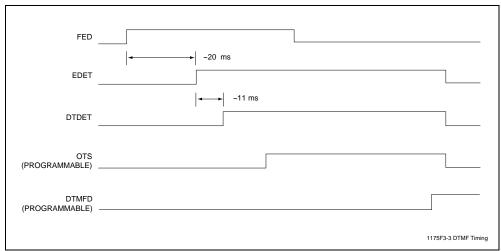

| Figure 3-3. DTMF Receiver Status Bit Timing                                     | 3-22 |

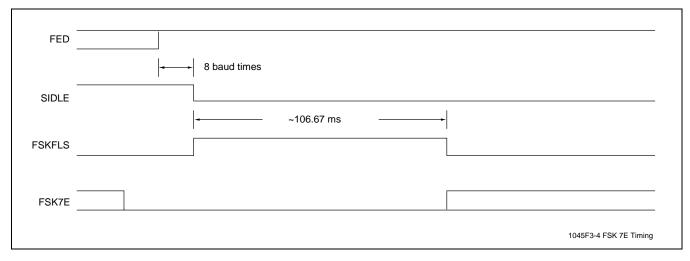

| Figure 3-4. FSK 7E Flag Detector Timing                                         | 3-23 |

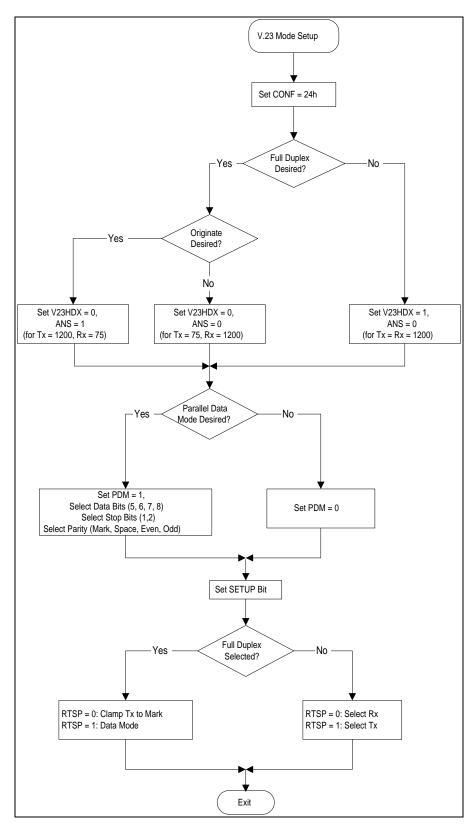

| Figure 3-5. V.23 Modes Setup Procedure                                          | 3-25 |

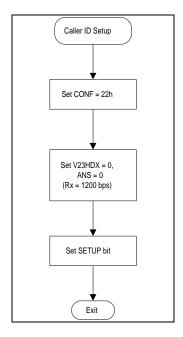

| Figure 3-6. Caller ID Mode Setup Procedure                                      | 3-26 |

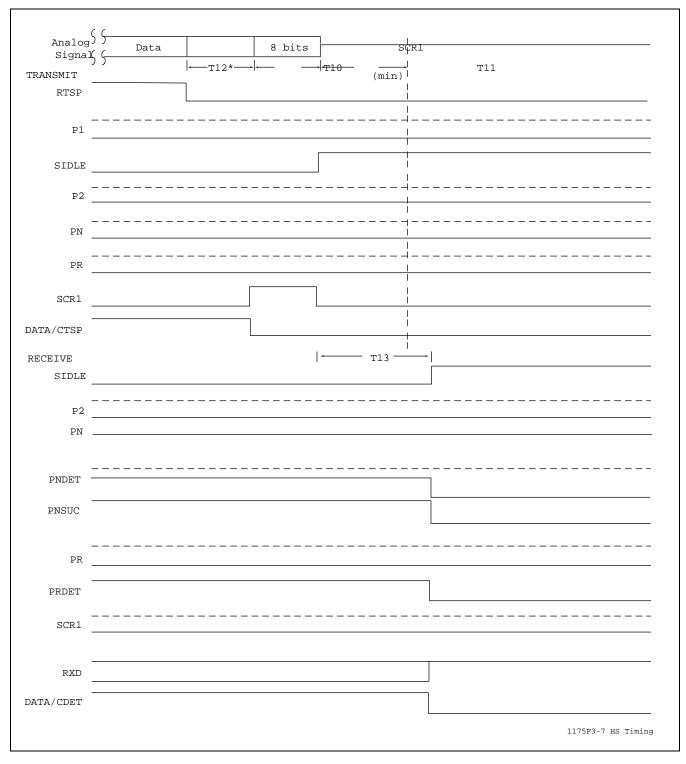

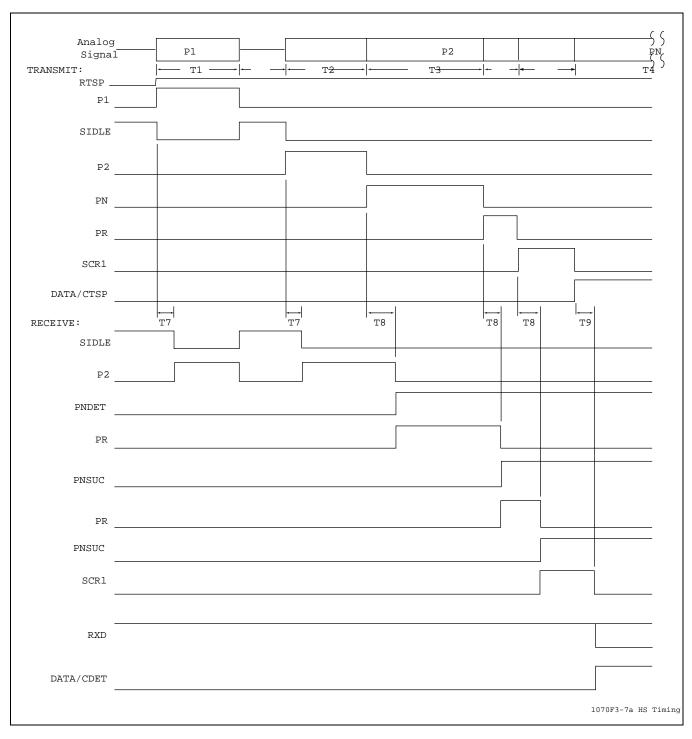

| Figure 3-7. High Speed Mode Status Bit Timing                                   | 3-27 |

| Figure 4-1. Host Flowchart - RAM Data Read and RAM Data Write                   | 4-5  |

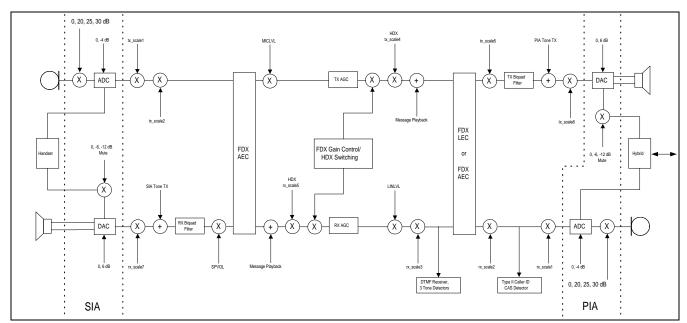

| Figure 4-2. PIA/SIA Signal Flow Control                                         | 4-20 |

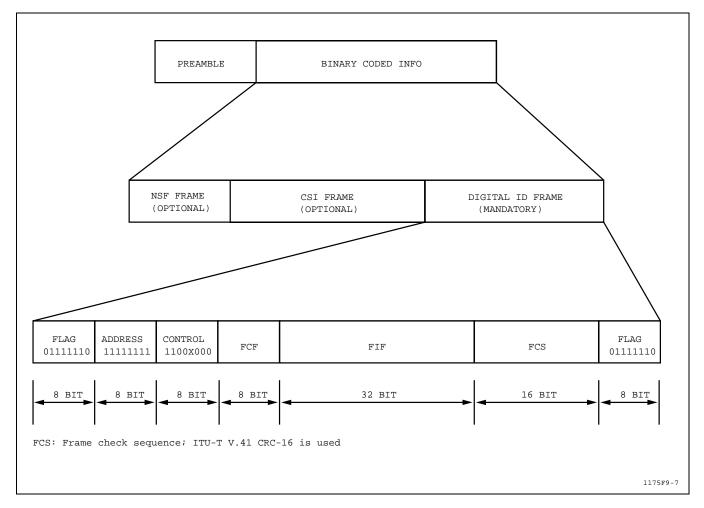

| Figure 5-1. HDLC Frame                                                          | 5-1  |

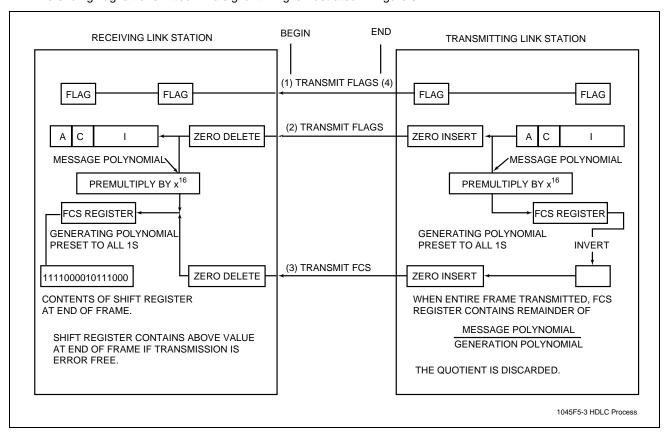

| Figure 5-2. CRC Polynomial Implementation                                       | 5-2  |

| Figure 5-3. HDLC Process.                                                       | 5-3  |

| Figure 5-4. HDLC Signal Timing                                                  | 5-4  |

| Figure 6-1. Modem Tone Detection Diagram                                        | 6-1  |

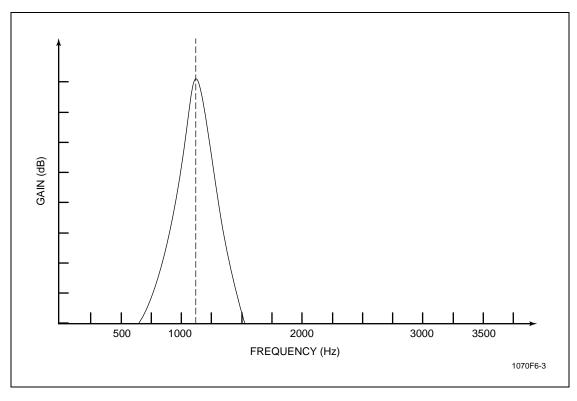

| Figure 6-2. Typical Single Filter Response                                      | 6-4  |

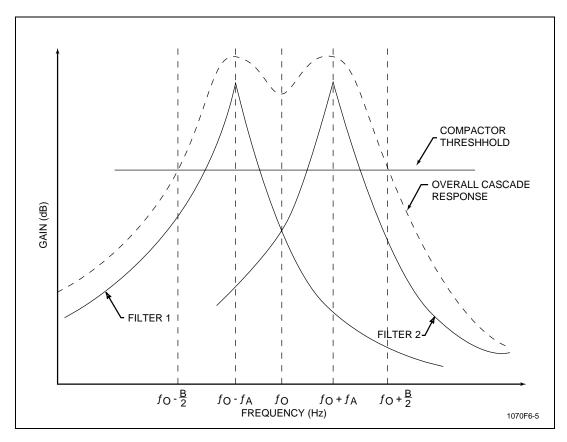

| Figure 6-3. Typical Cascade Filter Response                                     | 6-4  |

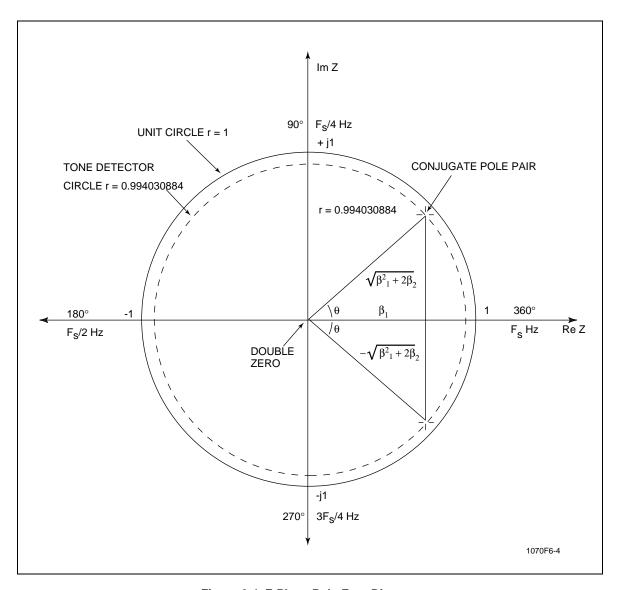

| Figure 6-4. Z-Plane Pole-Zero Diagram                                           | 6-5  |

| Figure 6-5. Bandwidth and Offset Frequencies                                    | 6-6  |

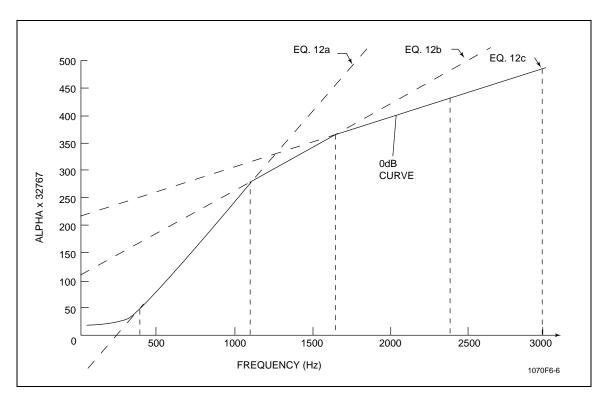

| Figure 6-6. Alpha-zero Center Frequency                                         | 6-6  |

| Figure 7-1. Autodialer Flowchart                                                | 7-5  |

| Figure 8-1. Coder Implementation                                                | 8-2  |

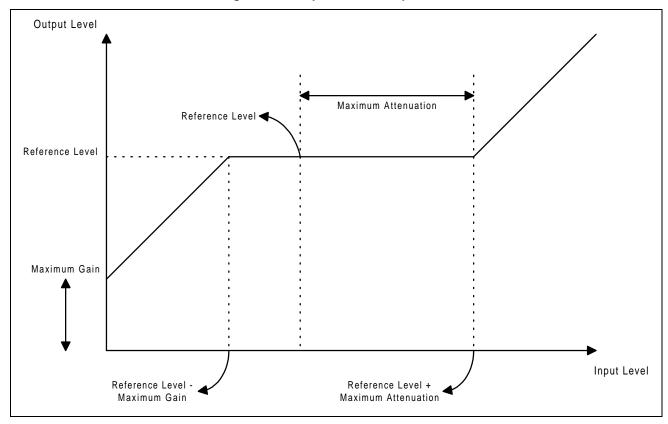

| Figure 8-2. Energy AGC and Classifier AGC Operation                             | 8-4  |

| Figure 8-3. AGC Implementation                                                  | 8-5  |

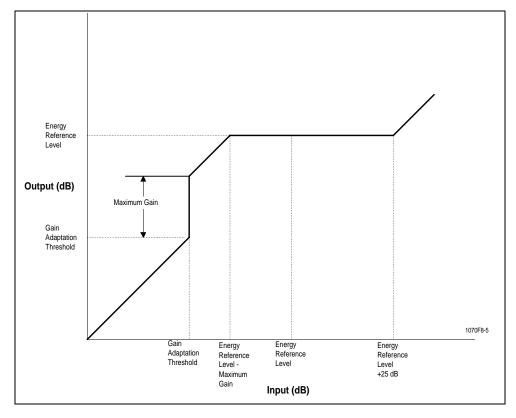

| Figure 8-4. Sample Rate AGC Operation                                           | 8-8  |

| Figure 8-5. Sample Rate AGC Parameters Operating Envelope                       | 8-8  |

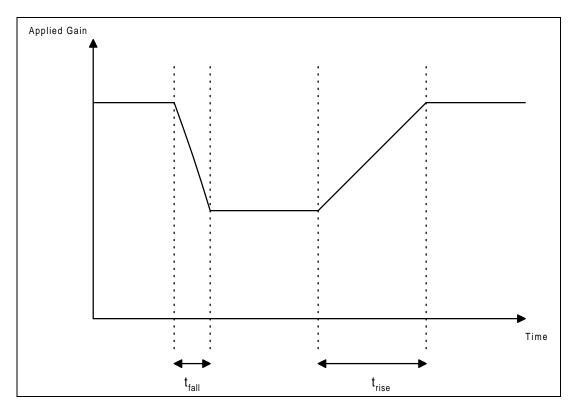

| Figure 8-6. Sample Rate AGC Slew Characteristics                                | 8-10 |

| Figure 8-7. Energy and Classifier AGC Parameters Operating Envelope             | 8-10 |

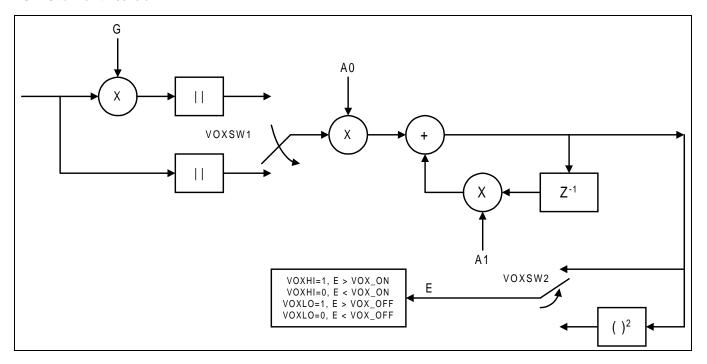

| Figure 8-8. Sample Rate VOX                                                     | 8-12 |

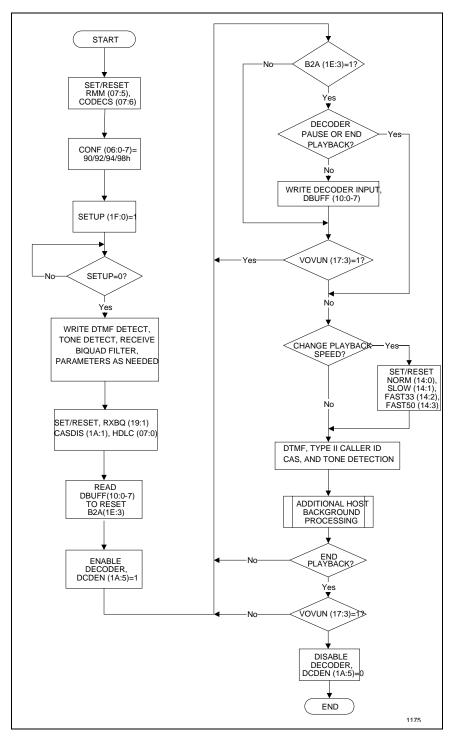

| Figure 8-9. Decoder Implementation                               | 8-15 |

|------------------------------------------------------------------|------|

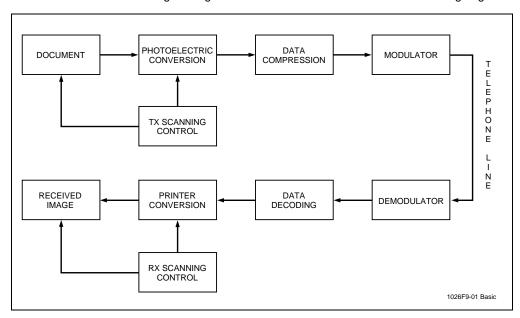

| Figure 9-1. Basic Block Diagram of G3 Facsimile                  | 9-2  |

| Figure 9-2. G3 Facsimile Procedure                               | 9-2  |

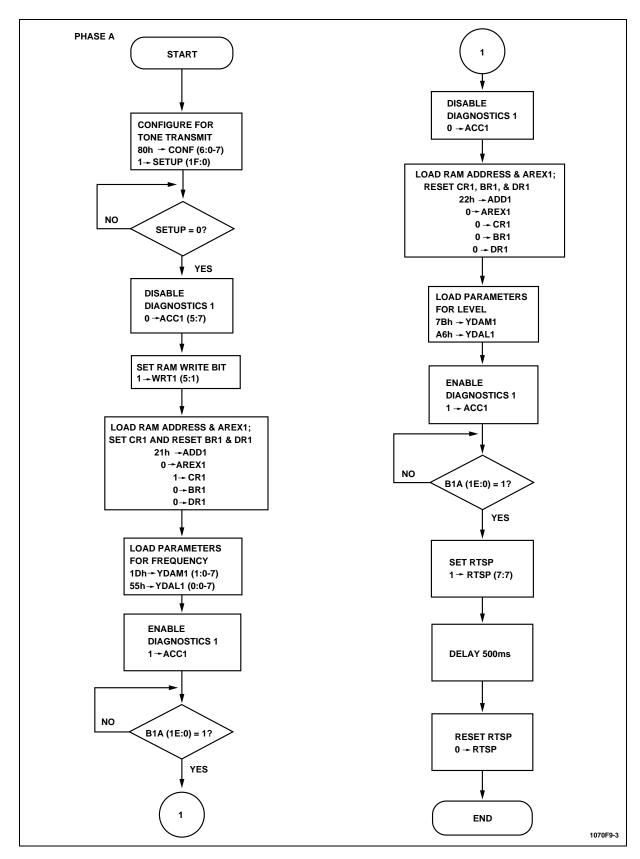

| Figure 9-3. Transmit Calling Tone (CNG) (1100 Hz)                | 9-3  |

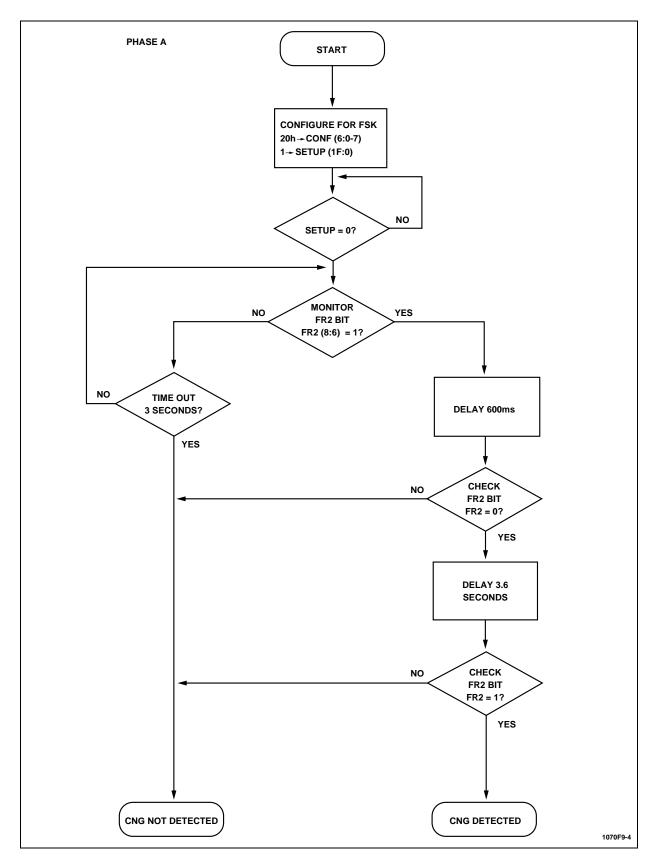

| Figure 9-4. Detecting CNG Tone (1100 Hz)                         | 9-4  |

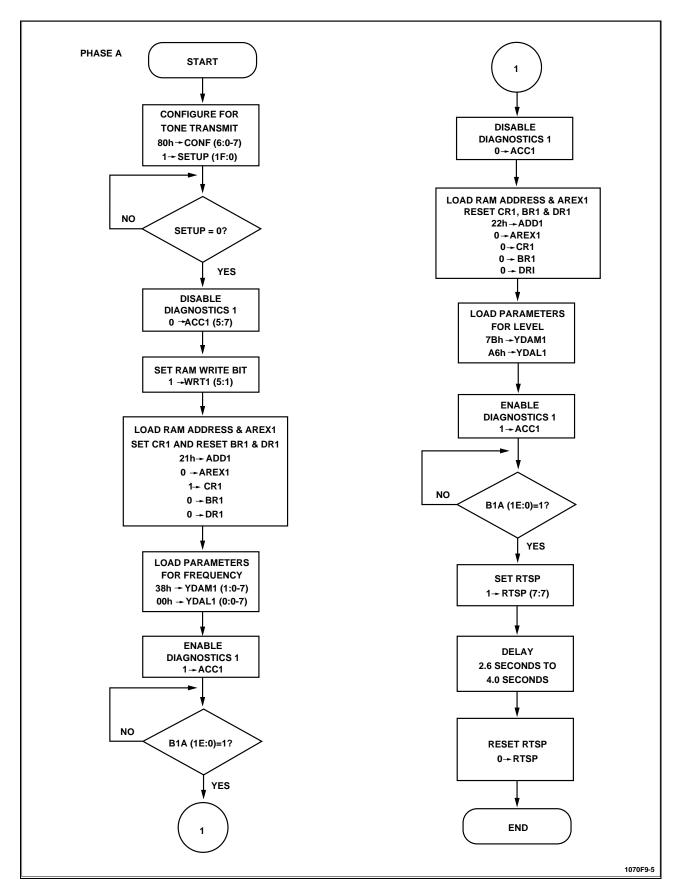

| Figure 9-5. Transmit Called Tone (CED) (2100 Hz)                 | 9-5  |

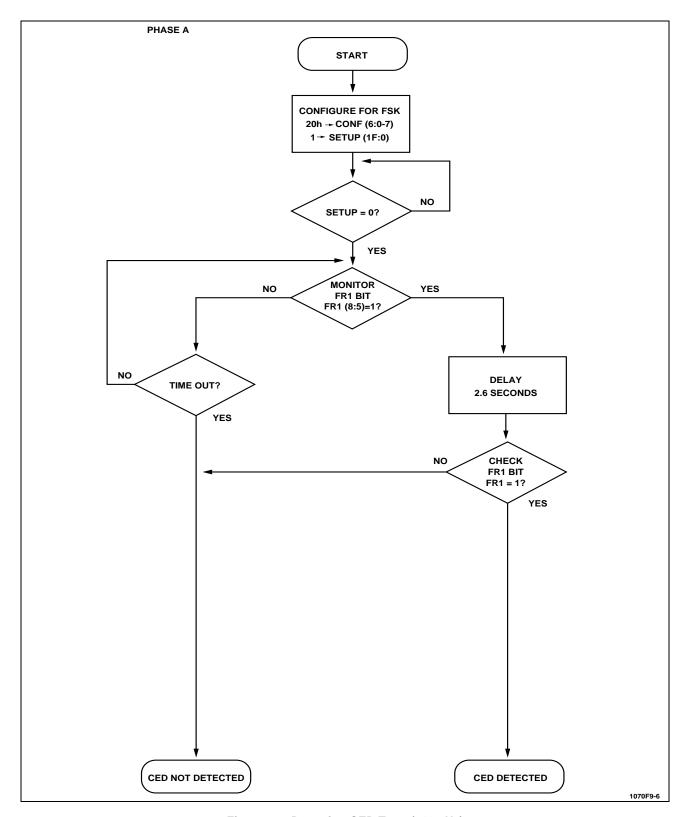

| Figure 9-6. Detecting CED Tone (2100 Hz)                         | 9-6  |

| Figure 9-7. HDLC Frame Structure                                 | 9-7  |

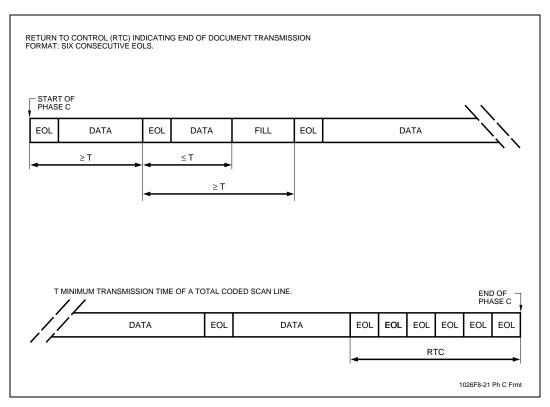

| Figure 9-8. Phase C Format                                       | 9-9  |

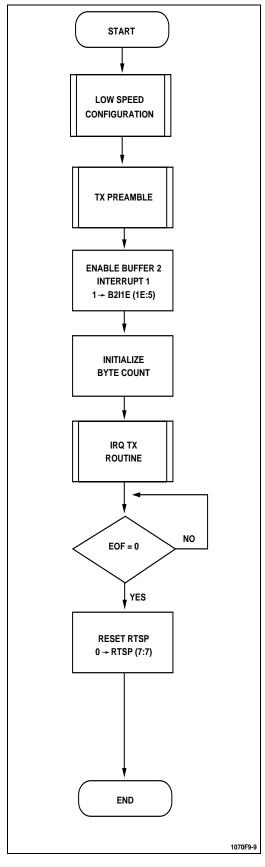

| Figure 9-9. Transmit FSK/HDLC Signals                            | 9-10 |

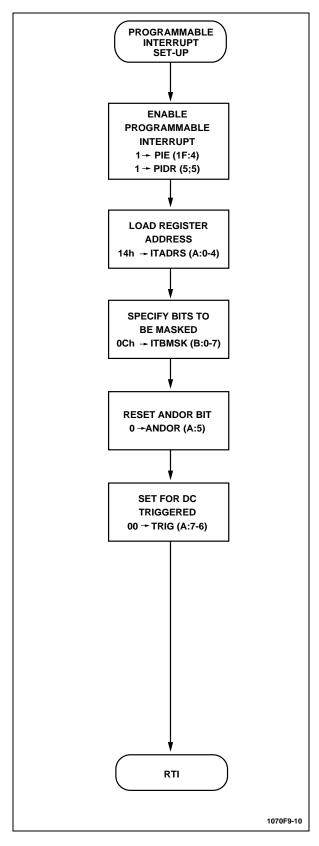

| Figure 9-10. Setup for Programmable Interrupt                    | 9-11 |

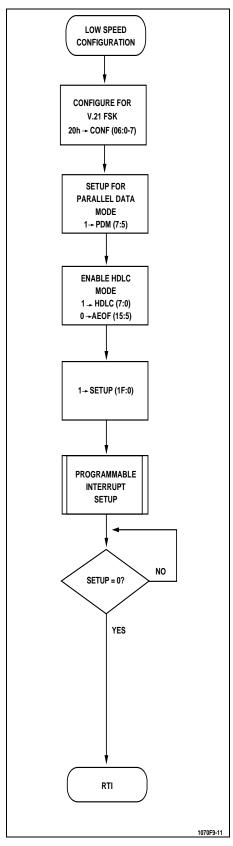

| Figure 9-11. Low Speed Configuration Subroutine                  | 9-12 |

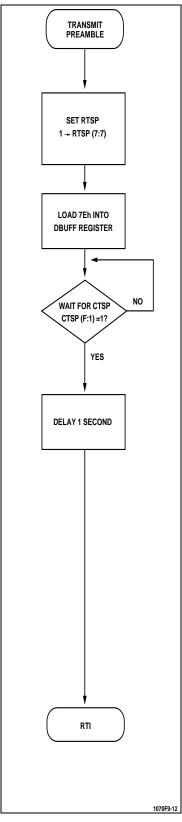

| Figure 9-12. Transmit Preamble                                   | 9-13 |

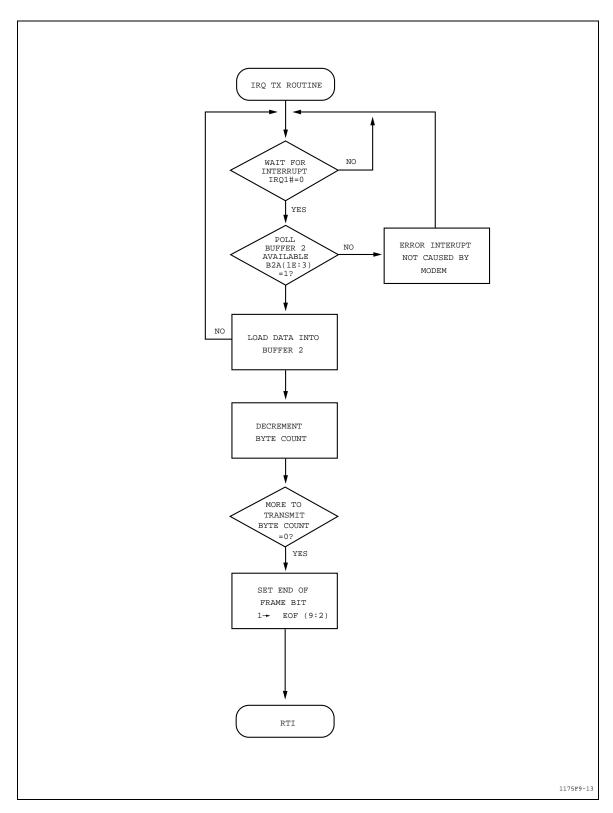

| Figure 9-13. Low Speed Interrupt-Driven Transmit                 | 9-14 |

| Figure 9-14. Receive FSK/HDLC Signals                            | 9-15 |

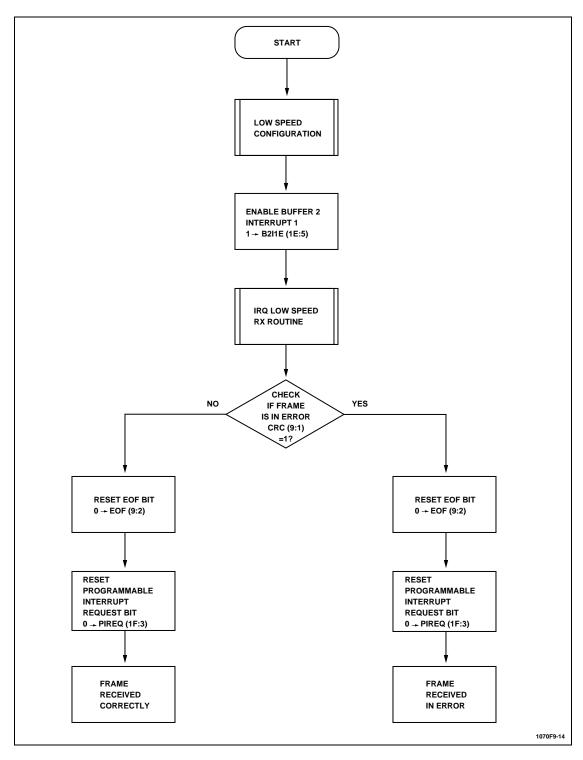

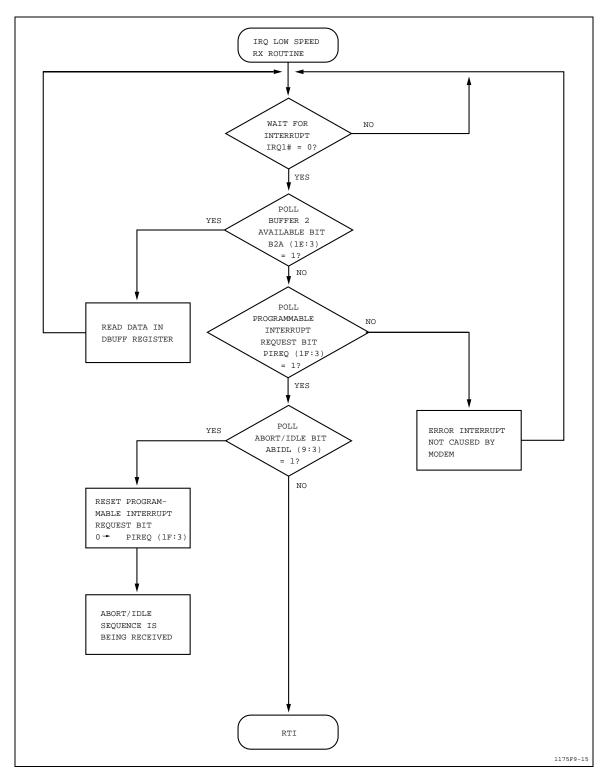

| Figure 9-15. Low Speed Interrupt-Driven Receive                  | 9-16 |

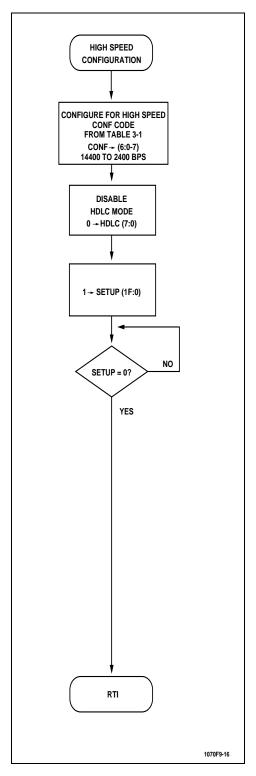

| Figure 9-16. High Speed Configuration Setup                      | 9-17 |

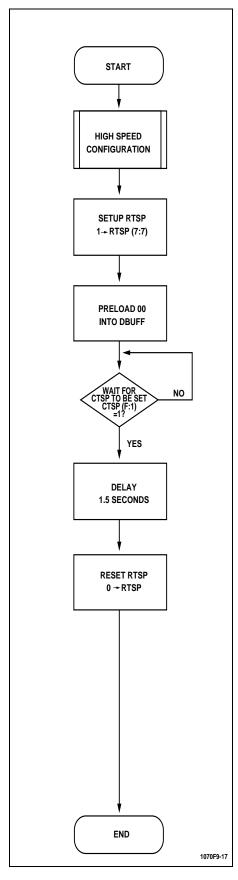

| Figure 9-17. Transmitting TCF                                    | 9-18 |

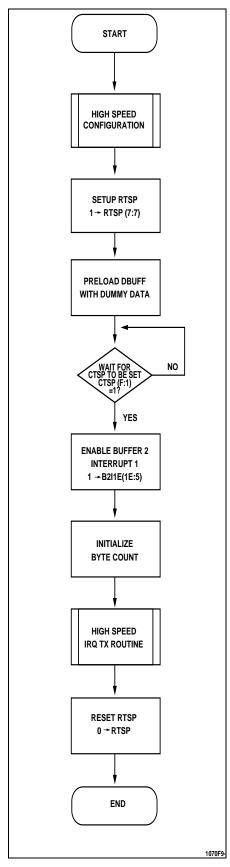

| Figure 9-18. High Speed Message Transmission                     | 9-19 |

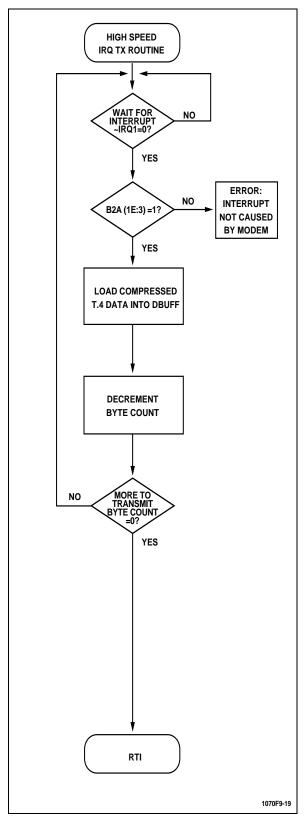

| Figure 9-19. High Speed Interrupt-Driven Transmit                | 9-20 |

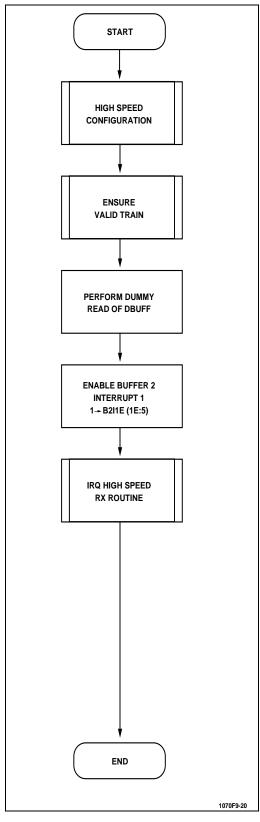

| Figure 9-20. High Speed Reception Setup                          | 9-21 |

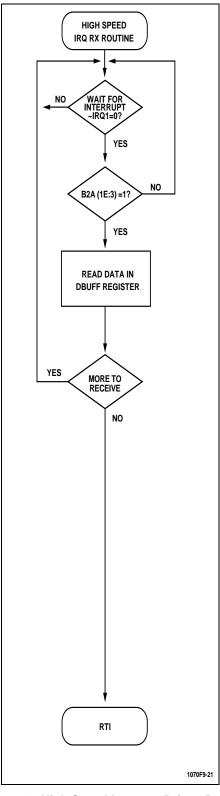

| Figure 9-21. High Speed Interrupt Driven Receive                 | 9-22 |

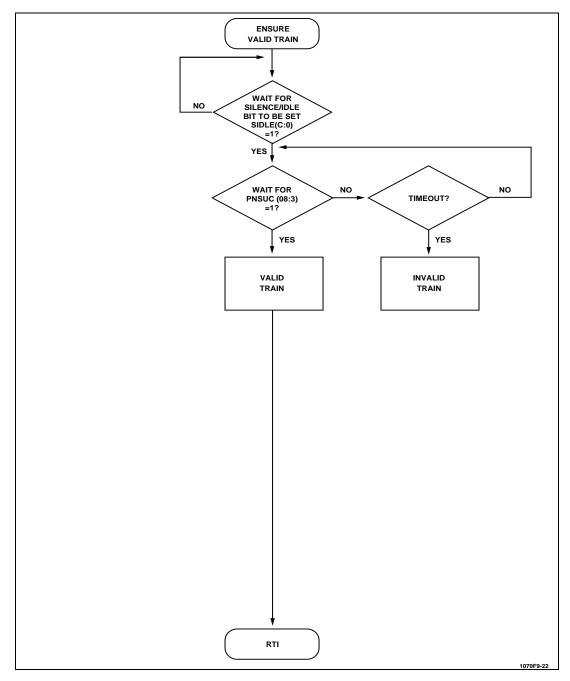

| Figure 9-22. Valid Training Sequence Check                       | 9-23 |

| Figure 9-23. ECM Frame Structure                                 | 9-25 |

| Figure 9-24. ECM Message Protocol Example                        | 9-26 |

| Figure 9-25. PPS and PPR Frame Structure                         | 9-27 |

| Figure 9-26. Signal Recognition Algorithm in High Speed Mode     | 9-29 |

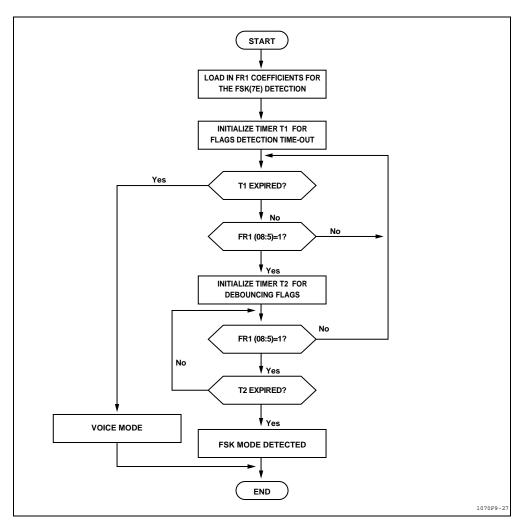

| Figure 9-27. FSK Signal Detection Algorithm in Voice Mode        | 9-30 |

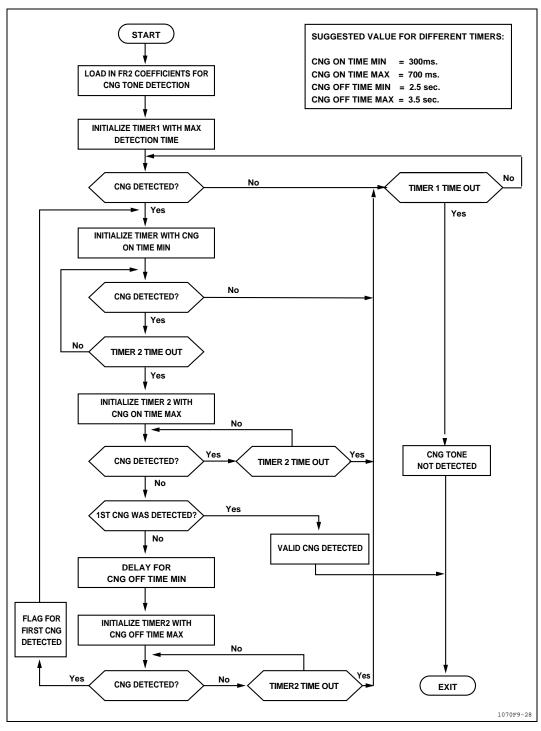

| Figure 9-28. CNG Detection (1100 Hz) in Voice Mode               | 9-31 |

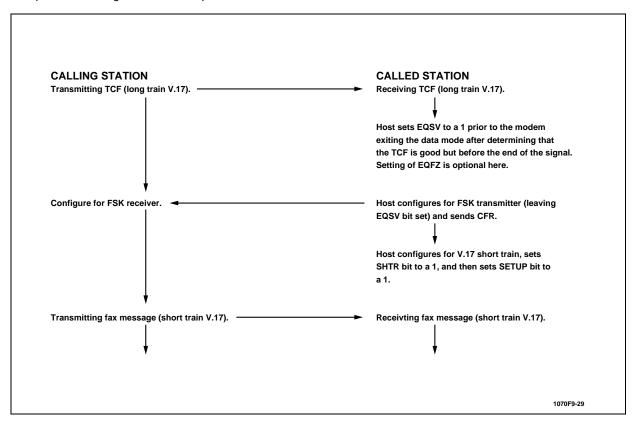

| Figure 9-29. Example V.17 Short Train Time Line                  | 9-32 |

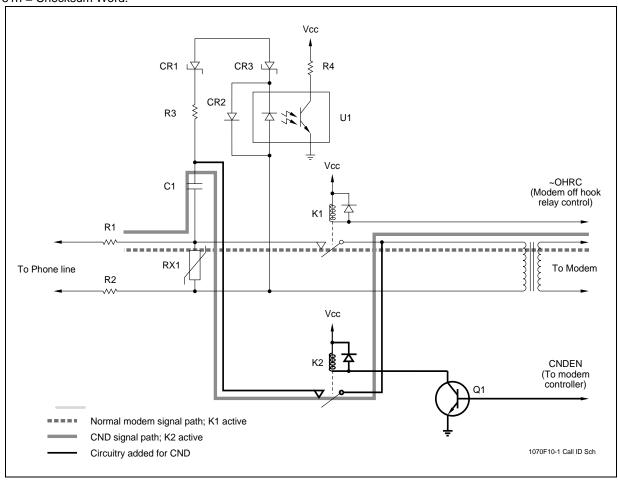

| Figure 10-1. DAA Circuit Supporting CND                          | 10-2 |

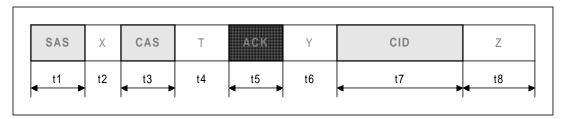

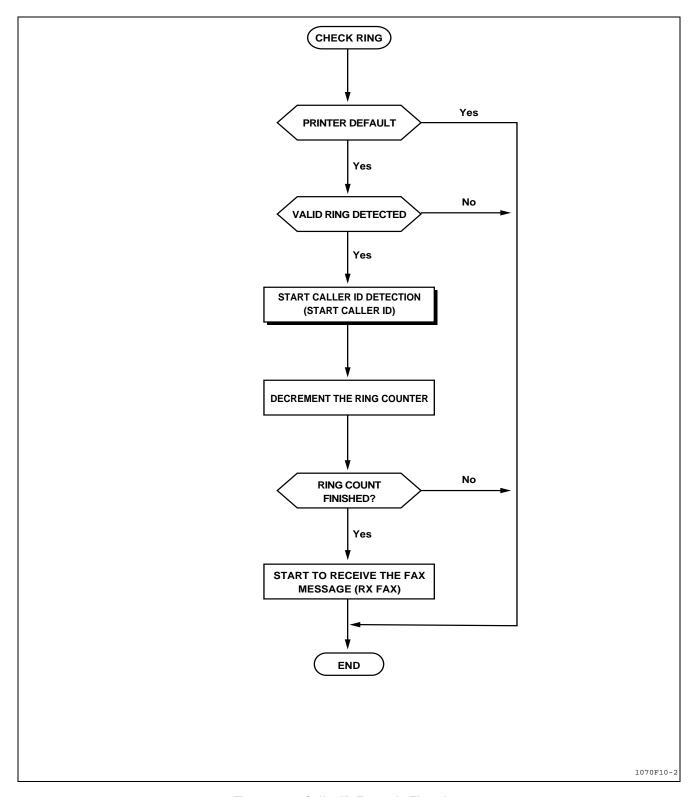

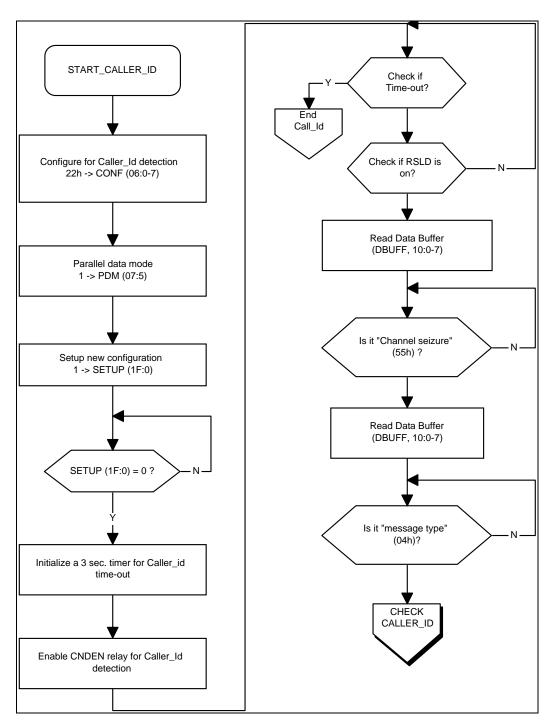

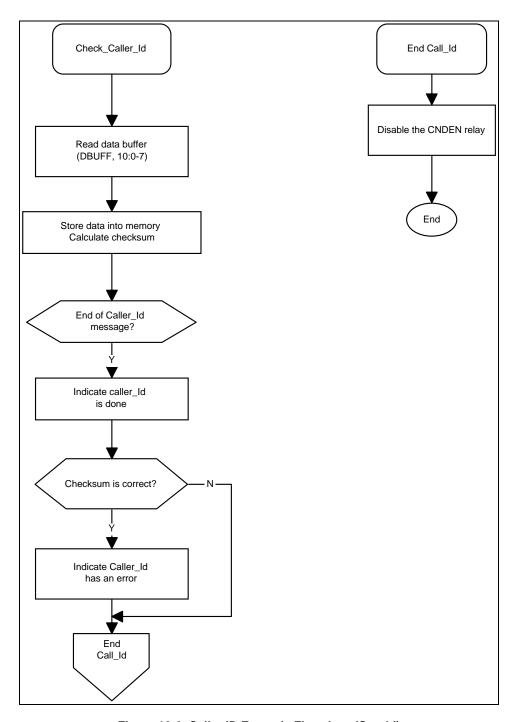

| Figure 10-2. Caller ID Example Flowchart                         | 10-5 |

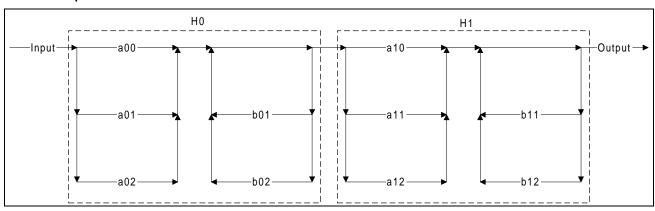

| Figure -11-1. PDE Block Diagram                                  | 11-2 |

| Figure 11-2. PDE Response                                        | 11-2 |

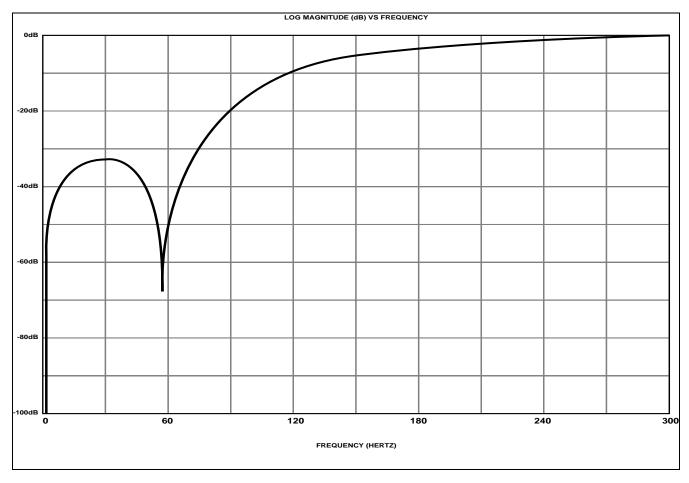

| Figure 11-3. Digital Cable Equalizer Frequency Response          | 11-3 |

| Figure 11-4. Receive Path Frequency Response without HPF         | 11-4 |

| Figure 11-5. Receive Path Frequency Response with HPF            | 11-5 |

| Figure 12-1. Speakerphone Diagram                                | 12-2 |

| Figure 13-1. Typical Bit Error Rate (BER) Curves (V.29 and V.27) | 13-3 |

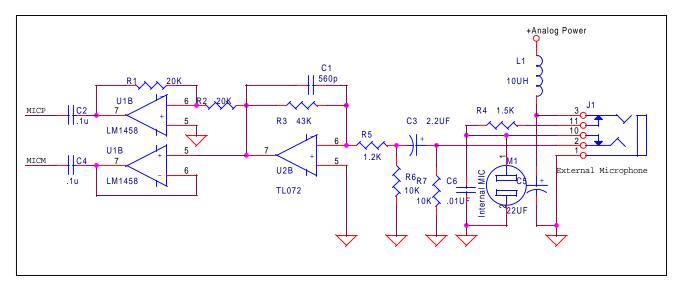

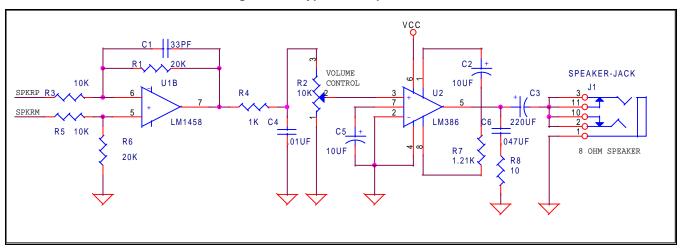

| Figure 14-1. Fax/DTAM Interface Circuit           | 14-2 |

|---------------------------------------------------|------|

| Figure 14-2. Fax Speakerphone Interface Circuit   | 14-3 |

| Figure 14-3. Typical Interface to External Hybrid | 14-4 |

| Figure 14-4. Typical Microphone Circuit           | 14-5 |

| Figure 14-5. Typical Speaker Circuit              | 14-5 |

| Figure 15-1, 128-Pin TOFP Dimensions              | 15-1 |

1175 ix

# **List of Tables**

| Table 1-1. Modem Models and Supported Features                | 1-2   |

|---------------------------------------------------------------|-------|

| Table 1-2. V.23 Default Turn-On and Turn-Off Sequences        | 1-6   |

| Table 1-3. Configurations, Signaling Rates, and Data Rates    | 1-7   |

| Table 1-4. Turn-On Sequence Times                             | 1-7   |

| Table 1-5. Turn-Off Sequence Times                            | 1-7   |

| Table 2-1. FM209/214 Modem Pin Signals - 128-Pin TQFP         | 2-6   |

| Table 2-2. Modem Hardware Interface Signal Definitions        | 2-8   |

| Table 2-3. Digital Electrical Characteristics                 | 2-13  |

| Table 2-4. Analog Electrical Characteristics                  | 2-14  |

| Table 2-5. Current and Power Requirements                     | 2-15  |

| Table 2-6. Absolute Maximum Ratings                           | 2-15  |

| Table 2-7. Microprocessor Interface Timing                    | 2-17  |

| Table 3-1. Interface Memory Bit Definitions                   | 3-3   |

| Table 3-2. High Speed Status Bit Timing                       | 3-26  |

| Table 3-3. Power-On Reset Self-Test Values                    | 3-29  |

| Table 3-4. RAM Access Codes                                   | 3-29  |

| Table 4-1. Modem DSP RAM Access Codes                         | 4-3   |

| Table 5-1. Transmitter and Receiver Initialization            | 5-5   |

| Table 6-1. Filter Coefficient RAM Access Codes                | 6-7   |

| Table 6-2. Calculated Coefficient Values, 9600 Hz Sample Rate | 6-8   |

| Table 6-3. Calculated Coefficient Values, 8000 Hz Sample Rate | 6-9   |

| Table 7-1. DTMF Signals                                       | 7-1   |

| Table 7-2. DTMF Parameters                                    | 7-3   |

| Table 7-3. Common Single Tone Parameters                      | 7-5   |

| Table 9-1. FR3 Coefficient for 1650 Hz Detection              | 9-28  |

| Table 11-1. PDE Poles and Zeros                               | 11-3  |

| Table 11-2. PDE PRAM Access Codes                             | 11-3  |

| Table 12-1. Speakerphone RAM Access Codes - SBRAM             | 12-3  |

| Table 12-2. Register Location 0E Use                          | 12-12 |

| Table 12-3. Register Location 0F Use                          | 12-12 |

| Table 12-4. Register Location 18 Use                          | 12-13 |

| Table 12-5. Register Location 19 Use                          | 12-13 |

| Table 13-1. DTMF Receiver Performance Characteristics         | 13-2  |

| Table 14-1. Crystal Specifications - 32.256 Functional Mode   | 14-6  |

| Table 14-2. FM209/214 Modem Pin Noise Characteristics         | 14-8  |

#### 1. INTRODUCTION

The Rockwell FM209 and FM214 MONOFAX<sup>®</sup> facsimile modem family offers 9600 bps and 14400 bps half-duplex capability with options supporting voice and audio codecs, full-duplex and half-duplex speakerphone, speaker independent and speaker dependent automatic speech recognition, Type I and Type II Caller ID, and V.23 full duplex modes. The modem models are identified in Table 1-1.

These functions are supplied in a single device. The Rockwell FM209 and FM214 MONOFAX facsimile modem family is packaged in a 128-pin TQFP containing a Digital Signal Processor (DSP), a Primary Integrated Analog (PIA) codec, and a optional Secondary Integrated Analog (SIA) codec (-S option).

This device family enables cost-effective development of a common facsimile machine design featuring digital answering machine, full-duplex speakerphone and automatic speech recognition functionality.

#### 1.1 FACSIMILE MODEM

The modem can operate at 14400, 12000 (FM214 family only), 9600, 7200, 4800, 2400, or 300 bps, and can perform HDLC framing per T.30 at all rates. A programmable DTMF detector, three programmable tone detectors, V.21 Channel 2 FSK 7E flag detector, Caller ID demodulator and ring detector are provided.

#### 1.2 VOICE AND AUDIO CODECS (-V OPTION)

The voice coder/decoder (codec) compresses voice at an average rate of 2.9 kbps which provides 24 minutes of stored voice messages in 4 Mbits of memory. This voice codec allows the host controller to efficiently store and playback digital incoming messages (ICMs), outgoing messages (OGMs) and conversations (-VS option).

The ADPCM audio codec compresses audio signals (music/voice) at 32 kbps or 24 kbps and the PCM audio codec records audio signals at 128 kbps or 64 kbps for highest fidelity coding and reproduction.

Selectable error correction coding allows storage in audio grade RAMs (ARAMs). Echo cancellation techniques employed during playback allow DTMF, tone and Type II Caller ID CAS detection during voice/audio codec operation to support user selectable features. The coder can record messages from the PIA or SIA. The decoder can play back messages to the PIA or both the PIA and SIA. Dual/single tone transmission is available when the decoder is disabled.

#### 1.3 SPEAKERPHONE (-S OPTION)

The full-duplex speakerphone provides hands-free telephone voice communication employing acoustic echo cancellation and line echo cancellation. It also supports full-duplex intercom voice communication employing dual acoustic echo cancellation techniques. The half-duplex speakerphone provides hands-free telephone/intercom voice communication with exceptionally high gain.

Conversation recording and message playback are supported during speakerphone operation (-VS option). Also supported are DTMF detector, tone detectors, and Caller ID Type II CAS detection.

The speakerphone algorithm constantly adjusts its parameters to deliver the best performance during real-time conditions, allowing automatic fallback from full-duplex to pseudo-duplex. The host controller can easily set up the speaker mute, microphone mute, automatic gain control (AGC) enable/disable, microphone level, line level, speaker volume, tone transmit, and handset functions.

#### 1.4 AUTOMATIC SPEECH RECOGNITION (-R OPTION)

The Automatic Speech Recognition (ASR) consists of the following:

- Speaker Independent (SI) North American English isolated word recognition for a predefined 69-word vocabulary list.

- Speaker Dependent (SD) isolated word training.

- · SD isolated word recognition functions.

More information on ASR features is available in an Application Note. Contact your sales representative.

#### 1.5 V.23 FULL-DUPLEX MODEM AND CALLER ID

Both full-duplex transmit and receive (with asymmetric 1200/75 bps connection) and half-duplex (1200 bps) asynchronous V.23 are supported, as well as both serial and parallel interfaces to the modem. The V.23 algorithm includes an optional, programmable, receive compromise equalizer which is active in both V.23 and Caller ID (V.23 Receive only) modes.

Common applications for V.23 include France's Minitel and Japan's Lowest Cost Routing.

**Table 1-1. Modem Models and Supported Features**

| Modem     | Max. Data<br>Rate | Voice and Audio<br>Codecs<br>(-V) | FDX/HDX Digital<br>Speakerphone<br>(-S) | Automatic Speech<br>Recognition<br>(-R) |

|-----------|-------------------|-----------------------------------|-----------------------------------------|-----------------------------------------|

| FM214-VSR | 14.4 kbps         | •                                 | •                                       | •                                       |

| FM214-VS  | 14.4 kbps         | •                                 | •                                       | -                                       |

| FM214-V   | 14.4 kbps         | •                                 | -                                       | -                                       |

| FM214     | 14.4 kbps         | -                                 | -                                       | -                                       |

| FM209-VSR | 9.6 kbps          | •                                 | •                                       | •                                       |

| FM209-VS  | 9.6 kbps          | •                                 | •                                       | -                                       |

| FM209-V   | 9.6 kbps          | •                                 | -                                       | -                                       |

| FM209     | 9.6 kbps          | -                                 | -                                       | -                                       |

#### 1.6 FEATURES

- · Group 3 facsimile transmission/reception

- ITU-T V.17 and V.33 (FM214 models)

- ITU-T V.29, V.27 ter, T.30, V.21 Channel 2, T.4

- ITU-T V.17 and V.27 ter short train

- HDLC framing at all speeds

- Receive dynamic range: 0 dBm to –43 dBm

- Automatic adaptive equalization

- Fixed and programmable digital compromise equalization

- DTMF detect and tone detect

- ITU-T V.21 Channel 2 FSK 7E Flag Detect

- Ring detector

- Programmable transmits level

- Programmable single/dual tone transmission

- · Voice codec (-V Option)

- 24 minutes of voice storage per 4 Mbit memory

- Near toll quality voice recording and playback

- Programmable AGCs

- Programmable line/microphone input and line/speaker output filters

- Error correction coding allows ARAM usage

- DTMF detect, tone detect, and tone transmit

- Type II Caller ID CAS detection

- Pitch synchronized fast and slow playback

- Near-end echo cancellation

- ADPCM Audio codec (-V Option)

- High fidelity recording and playback of audio signals

- 32 kbps and 24 kbps

- Programmable AGCs

- Programmable line/microphone input and line/speaker output filters

- DTMF detect, tone detect, and tone transmit

- Type II Caller ID CAS detection

- Near-end echo cancellation

- · PCM audio codec

- 128 kbps and 64 kbps

- DTMF detect and tone detect

- Type II Caller ID CAS detection

- Near end echo cancellation

- Full-duplex speakerphone (-S Option)

- Acoustic echo cancellation

- Line echo cancellation or secondary acoustic echo cancellation

- Programmable microphone and speaker AGCs

- Programmable line and speaker output filters

- Microphone and speaker volume control and muting

- Auto fallback toward pseudo-duplex operation under poor operating conditions

- Programmable handset echo simulation in handset operation

- High gain half-duplex mode

- Intercom support

- DTMF detect and 3 tone detectors

- Type II Caller ID CAS detection

- Two dual tone transmitters

- Conversation recording and message playback with Voice or ADPCM Audio codec (-VS option)

- Automatic Speech Recognition (-R Option). More information is provided in an Application Note. Contact your sales representative.

- Speaker Dependent (SD) and Speaker Independent (SI) isolated word recognition

- SI Vocabulary (English) for hands-free voice control of dialing, telephone answering machine and fax functions

- Active word list for recognition selected by host controller

- Supports input from microphone, local handset, and telephone line

- SI word models trained off-line and stored in DSP ROM

- SD word models trained in real-time, stored in (off-chip) NVRAM and downloaded to DSP RAM

- Supports 30 Active simultaneous SD words

- SD training single utterance or multiple utterances

- 2.5 second maximum speech length for SD training

- Rejection capability provided for SI mode

- · Room Monitor

- DTMF detect, tone detect and tone transmit

- Type II Caller ID CAS detection

- Near end echo cancellation

- Monitor recording and message playback with Voice or Audio Codec (-V option)

- V.23 and Type I Caller ID

- Full-duplex modes:

- TX = 75 bps, RX = 1200 bps

- TX = 1200 bps, RX = 75 bps

- Half-duplex mode:

- TX = RX = 1200 bps

- Serial and parallel data modes

- Programmable parallel data mode

- 5, 6, 7, or 8 data bits

- 1 or 2 Stop bits

- Mark, Space, Even, or Odd Parity

- Break function

- Transmitter squelch

- Compromise equalizer

- Programmable interface memory interrupt

- Eight General Purpose Input (GPI) and eight General Purpose Output (GPO) pins for host assignment

- DTE interface: two alternate ports

- Selectable microprocessor bus (6500 or 8085)

- ITU-T V.24 (EIA/TIA-232-E compatible) interface

- · TTL and CMOS compatible

- · 3.3V/5V operation

- Power consumption (see Table 2-5):

- Operating Mode: 200 mW (Basic), 275 mW (-V option), 300 mW (-VS option)

- Sleep Mode: 1 ma (Basic, -V option, and -VS option)

- Packaging

- 128-pin TQFP (thin quad flat pack)

#### 1.7 TECHNICAL SPECIFICATIONS

#### 1.7.1 **Modem**

| Function                                       | Description                                                                                                                                                                                                                                             |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configurations, Signaling Rates and Data Rates | The selectable modem configurations, along with the corresponding symbol (baud) rates and data rates, are listed in Table 1-3.                                                                                                                          |

| Scrambler/Descrambler                          | The modem incorporates a self-synchronizing scrambler/descrambler in accordance with ITU-T V.17 (FM214 models), V.33 (FM214 models), V.29, and V.27 ter recommendations, depending on the selected configuration.                                       |

| Data Encoding                                  | Data encoding conforms to ITU-T recommendations V.17 ter (FM214 models), V.33 (FM214 models), V.29, V.27 ter, V.21 Channel 2, V.23 and CID receive.                                                                                                     |

| Fixed Digital Cable Compromise Equalizer       | Compromise equalization can improve performance when operating over low quality lines. The modem has a selectable fixed digital compromise cable equalizer in the high speed receive and transmit data paths.                                           |

|                                                | The modem includes an optional host programmable Receive Compromise Equalizer for V.23 1200 bps reception and Caller ID mode.                                                                                                                           |

| Transmitted Data Spectrum                      | Transmitted data spectrum is shaped in the baseband by an excess bandwidth finite impulse response filter (FIR) with the following characteristics:                                                                                                     |

|                                                | When operating at 2400 baud, the transmitted spectrum is shaped by a square root of 20% raised cosine filter.                                                                                                                                           |

|                                                | When operating at 1600 baud, the transmitted spectrum is shaped by a square root of 50% raised cosine filter.                                                                                                                                           |

|                                                | When operating at 1200 baud, the transmitted spectrum is shaped by a square root of 90% raised cosine filter.                                                                                                                                           |

|                                                | The out-of-band transmitter energy levels in the 4 kHz – 50 kHz frequency range is below –55.0 dBm.                                                                                                                                                     |

| Transmit Level                                 | The transmitter output (TXA) level is programmable in the DSP RAM from 0 dBm to –15.0 dBm. The modem adjusts the output level by digitally scaling the output to the transmitter's digital-to-analog converter.                                         |

| Turn-on Sequence                               | Transmitter turn-on sequence times are shown in Table 1-4.                                                                                                                                                                                              |

| Receive Dynamic Range                          | The receiver satisfies PSTN performance requirements for received line signal levels from 0 dBm to –43 dBm measured at the Receiver Analog Input (RXA) input. An external input buffer with 6 db loss recommended must be supplied between RXA and RIN. |

|                                                | The default values of the programmable Received Line Signal Detector (RLSD#) turn-on and turn-off threshold levels are –43 dBm and –48 dBm, respectively. The RLSD# threshold levels can be programmed over the following range:                        |

|                                                | Turn on: -10 dBm to -47 dBm                                                                                                                                                                                                                             |

|                                                | Turn off: -10 dBm to -52 dBm                                                                                                                                                                                                                            |

| Function                     | Description                                                                                                                                                              |

|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Automatic Adaptive Equalizer | An adaptive equalizer in ITU-T V.17 (FM214 models), V.33 (FM214 models), V.29 and V.27 ter modes compensates for transmission line amplitude and group delay distortion. |

| Receiver Timing              | The timing recovery circuit can track a $\pm 0.01\%$ frequency error in the associated transmit timing source.                                                           |

| Carrier Recovery             | The carrier recovery circuit can track a $\pm 7$ Hz frequency offset in the received carrier.                                                                            |

| Turn-off Sequence            | Transmitter turn-off sequence times are shown in Table 1-5                                                                                                               |

| Clamping                     | Received Data (RXD) is clamped to a constant mark whenever RLSD# is off.                                                                                                 |

| V.23 Modem                   | The modem can transmit and detect Break signals (continuous Space).                                                                                                      |

|                              | The Mark and Space frequencies are 1300 and 2100 Hz, respectively, for 1200 bps, and 390 and 450 Hz, respectively, for 75 bps.                                           |

|                              | The modem transmitter output can be forced to zero.                                                                                                                      |

|                              | The modem includes an optional host programmable Receive Compromise Equalizer for V.23 1200 bps reception and Caller ID Mode.                                            |

|                              | Default transmitter turn-on sequence time is shown in Table 1-2. See Section 4 for programming information.                                                              |

Table 1-2. V.23 Default Turn-On and Turn-Off Sequences

| Configuration | RTS On to CTS On | RTS Off to CTS Off |

|---------------|------------------|--------------------|

| V.23 FDX      | 10.5 ms          | 2.2 ms             |

#### 1.7.2 Tone Detectors and Generators

The tone detector signal path is separate from the main received signal path thus enabling tone detection to be independent of the receiver status. The tone detectors operate in all modes. The filter coefficients of each filter are host programmable in RAM.

The modem can generate voice-band single or dual tones from 0 Hz to 4800 Hz with a resolution of 0.15 Hz and an accuracy of 0.01%. Tones over 3400 Hz are attenuated. Dual tone generation allows the modem to operate as a programmable DTMF dialer.

Table 1-3. Configurations, Signaling Rates, and Data Rates

| Configuration                | Modulation <sup>1</sup> | Carrier<br>Frequency (Hz)<br>±0.01% | Data Rate (bps)<br>±0.01% | Baud<br>(Symbols/Sec.) | Bits<br>/Symbol | Constellation<br>Points |

|------------------------------|-------------------------|-------------------------------------|---------------------------|------------------------|-----------------|-------------------------|

| V.17/V.33 14400 <sup>2</sup> | TCM                     | 1700 or 1800                        | 14400                     | 2400                   | 6               | 128                     |

| V.17/V.33 12000 <sup>2</sup> | TCM                     | 1700 or 1800                        | 12000                     | 2400                   | 5               | 64                      |

| V.17 9600 <sup>2</sup>       | TCM                     | 1700 or 1800                        | 9600                      | 2400                   | 4               | 32                      |

| V.17 7200 <sup>2</sup>       | TCM                     | 1700 or 1800                        | 7200                      | 2400                   | 3               | 16                      |

| V.29 9600                    | QAM                     | 1700                                | 9600                      | 2400                   | 4               | 16                      |

| V.29 7200                    | QAM                     | 1700                                | 7200                      | 2400                   | 3               | 8                       |

| V.29 4800                    | QAM                     | 1700                                | 4800                      | 2400                   | 2               | 4                       |

| V.27 ter 4800                | DPSK                    | 1800                                | 4800                      | 1600                   | 3               | 8                       |

| V.27 ter 2400                | DPSK                    | 1800                                | 2400                      | 1200                   | 2               | 4                       |

| V.21 Channel 2 300           | FSK                     | 1650, 1850                          | 300                       | 300                    | 1               | _                       |

| V.23 receive HDX             | FSK                     | 1300, 2100                          | 1200                      | 1200                   | 1               | _                       |

| V.23 1200/75                 | FSK                     | 1300, 2100,<br>390, 450             | 1200/75                   | 1200/75                | 1               | _                       |

| Type I Caller ID             | FSK                     | 1200, 2200                          | 1200                      | 1200                   | 1               | -                       |

#### Notes:

Modulation legend:

QAM: Quadrature Amplitude Modulation

DPSK: Differential Phase Shift Keying

FSK: Frequency Shift Keying

TCM: Trellis-Coded Modulation

FM214 models only.

**Table 1-4. Turn-On Sequence Times**

|                               | RTS# On to CTS# On           |                             |  |  |  |

|-------------------------------|------------------------------|-----------------------------|--|--|--|

| Configuration                 | Echo Protector Tone Disabled | Echo Protector Tone Enabled |  |  |  |

| V.17/V.33                     | 1395 ms                      | 1602 ms                     |  |  |  |

| V.17 Short Train              | 144 ms                       | 351 ms                      |  |  |  |

| V.29 Long Train               | 255 ms                       | 443 ms                      |  |  |  |

| V.27 ter 4800 bps Long Train  | 710 ms                       | 917 ms                      |  |  |  |

| V.27 ter 4800 bps Short Train | 52 ms                        | 259 ms                      |  |  |  |

| V.27 ter 2400 bps Long Train  | 945 ms                       | 1152 ms                     |  |  |  |

| V.27 ter 2400 bps Short Train | 69 ms                        | 276 ms                      |  |  |  |

| V.21 Channel 2 300 bps        | ≤ 14 ms                      | ≤ 14 ms                     |  |  |  |

Table 1-5. Turn-Off Sequence Times

| Configuration                             | Data and Scrambled Ones | No Transmitted Energy | Total   |

|-------------------------------------------|-------------------------|-----------------------|---------|

| V.17 Long and Short Train/V.33            | 13.3 ms                 | 20 ms                 | 33.3 ms |

| V.29 Long Train                           | 5 ms                    | 20 ms                 | 25 ms   |

| V.27 ter 4800 bps Long and Short<br>Train | 7 ms                    | 20 ms                 | 27 ms   |

| V.27 ter 2400 bps Long and Short<br>Train | 10 ms                   | 20 ms                 | 30 ms   |

| V.21 Channel 2 300 bps                    | 7 ms                    | 0 ms                  | 7 ms    |

#### Notes:

- 1. In parallel data mode, the turn-off sequence may be extended by 8 bit times.

- 2. In HDLC mode, the turn-off sequence may be extended by more than 8 bit times.

#### 1.7.3 Voice Codec Mode (-V Option)

In the Voice Codec Mode, the modem can compress a voice message at an average rate of 2.9 kbps or at a fixed rate of 4.7 kbps and decompress a voice message at various pitch synchronized playback speeds. Optional error correction coding is available for use with ARAMs.

DTMF detect, tone detect, Type II Caller ID CAS detection and tone transmit functions are supported.

#### 1.7.4 ADPCM Audio Codec Mode (-V Option)

The ADPCM Audio Codec Mode enables the host to record and playback audio (music/voice) with highest fidelity. The modem can compress an audio signal to 32 kbps or 24 kbps.

DTMF detect, tone detect, Type II Caller ID CAS detection and tone transmit functions are supported.

#### 1.7.5 PCM Audio Codec Mode

The PCM Audio Codec Mode enables the host to transmit and receive 8-bit or 16-bit audio signals. In this mode, the host can access the analog-to-digital (A/D) converter (ADC) and the digital-to-analog (D/A) converter (DAC). Incoming analog audio signals can then be converted to digital format and digital signals can be converted to analog audio output.

DTMF detect, tone detect, Type II Caller ID CAS detection and tone transmit are supported.

#### 1.7.6 Speakerphone Mode (-S Option)

The speakerphone Mode provides hands-free full-duplex or half-duplex telephone operation and intercom operation under host control. The host can separately control volume, muting, AGC, and tone generation in microphone and speaker channels. The speakerphone automatically recalculates loop control parameters to maintain duplexity and stability.

Conversation recording and message playback with voice codec or ADPCM audio codec are supported (-V option). DTMF detect, tone detect and Type II Caller ID CAS detection are also supported.

#### 1.7.7 Automatic Speech Recognition (-R Option)

The Automatic Speech Recognition (-R option) performs of the following:

- Speaker Independent (SI) North American English isolated word recognition for a predefined 69-word vocabulary list

- Speaker Dependent (SD) isolated word training

- SD isolated word recognition functions

More information on ASR is available in an Application Note. Contact your sales representative.

#### 1.7.8 Room Monitor Mode

The Room Monitor Mode allows the remote-end user to monitor the local room activity by listening to audio captured by the microphone connected to the microphone input of IA. Room monitor operation is supported in Voice Codec Mode and ADPCM Audio Codec Mode for room monitor recording and OGM playback.

DTMF detect, tone detect, Type II Caller ID CAS detection and tone transmit are supported.

#### 2. HARDWARE INTERFACE SIGNALS

Any point that is active when exhibiting the relatively more negative voltage of a two-voltage system (0 VDC for TTL or –12 VDC for EIA/TIA-232-E) is called active low and is represented by a small circle at the signal point. Active low signals are indicated by a pound symbol (#). For example: RESET#. Edge-triggered clocks are indicated by a small triangle (DCLK). Open-collector (open-source or open-drain) outputs are denoted by a small half circle (signal IRQ1#).

A clock intended to activate logic on its rising edge (low-to-high transition) is called active high, while a clock intended to activate logic on its falling edge (high-to-low transition) is called active low. When a clock input is associated with a small circle, the input activates on a falling edge. If no circle is shown, the input activates on a rising edge.

| Description                                                        | Table / Figure         |

|--------------------------------------------------------------------|------------------------|

| Modem Functional Interconnect Diagram (Fax)                        | Figure 2-1             |

| Modem Functional Interconnect Diagram (Fax and DTAM)               | Figure 2-2             |

| Modem Functional Interconnect Diagram (Fax, DTAM and Speakerphone) | Figure 2-3             |

| FM209/214 Pin Assignments                                          | Figure 2-4             |

| Hardware Interface Signals (by pin)                                | Table 2-1              |

| FM209/214 Hardware Interface Signals                               | Table 2-2              |

| Digital Signal Interface Characteristics                           | Table 2-3              |

| Analog Signal Interface Characteristics                            | Table 2-4              |

| Power Consumption                                                  | Table 2-5              |

| Absolute Maximum Ratings                                           | Table 2-6              |

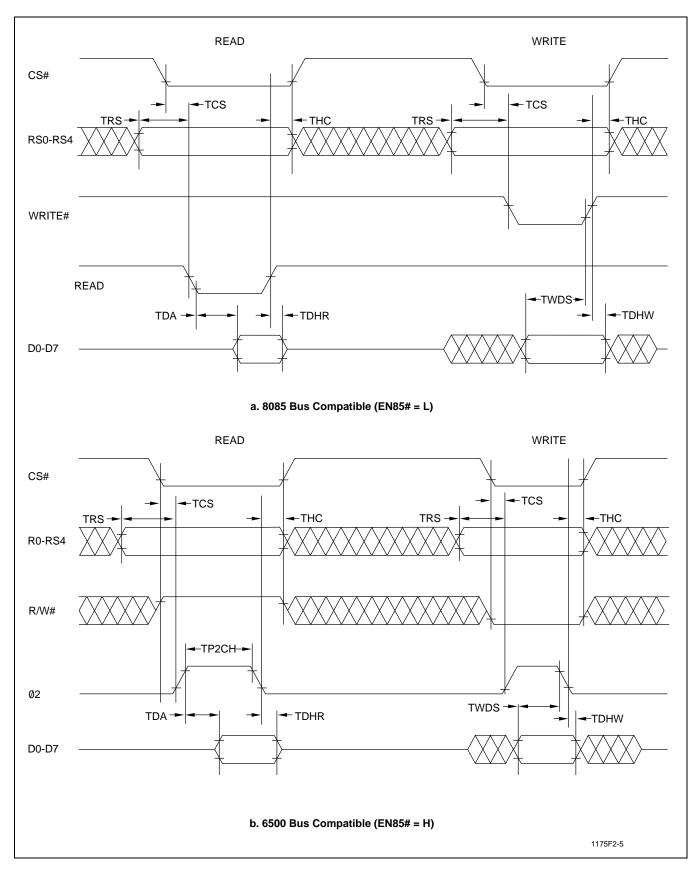

| Microprocessor Host Bus Interface Waveforms                        | Figure 2-5             |

| Microprocessor Host Bus Timing                                     | Table 2-7              |

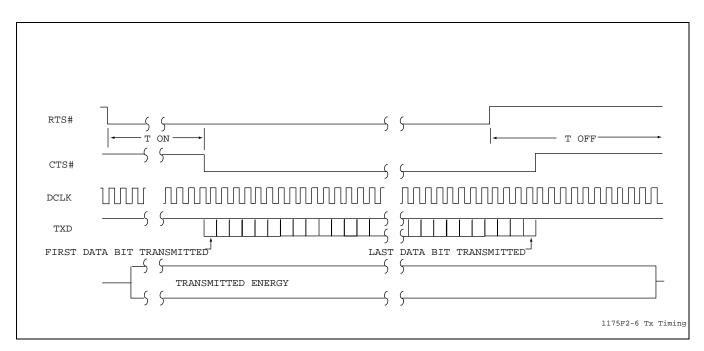

| Serial DTE Interface Waveforms                                     | Figure 2-6, Figure 2-7 |

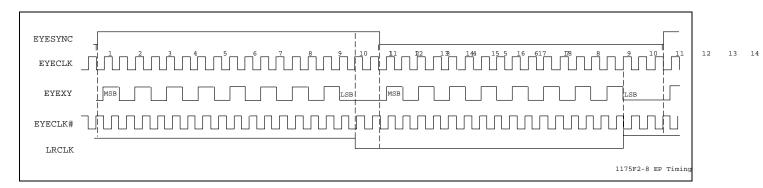

| Eye Pattern Timing                                                 | Figure 2-8             |

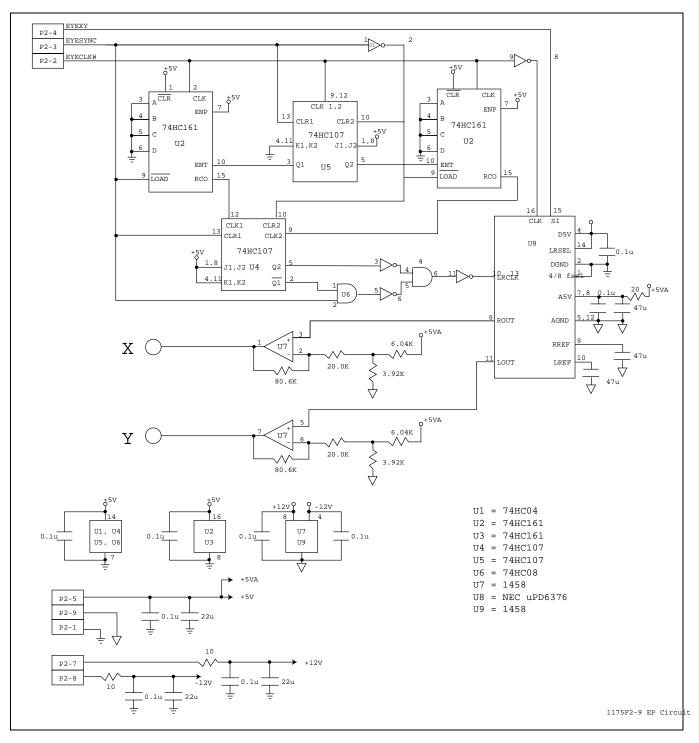

| Eye Pattern Circuit                                                | Figure 2-9             |

Figure 2-1. Modem Functional Interconnect Diagram (Fax)

Figure 2-2. Modem Functional Interconnect Diagram (Fax and DTAM)

Figure 2-3. Modem Functional Interconnect Diagram (Fax, DTAM, and Speakerphone)

Figure 2-4. Modem Pin Signals - 128-Pin TQFP

Table 2-1. FM209/214 Modem Pin Signals - 128-Pin TQFP

| Din | Signal Label    | I/O Turno | Interfore                   | Pin | Ciamal Label | I/O Tumo | Interfoce                   |

|-----|-----------------|-----------|-----------------------------|-----|--------------|----------|-----------------------------|

| Pin | _               | I/O Type  | Interface                   |     | Signal Label | I/O Type | Interface                   |

| 1   | SR4IN/RESERVED  | MI        | Modem Interconnect          | 51  | MCLK_P       | MI       | Modem Interconnect          |

| 2   | SR3OUT/RESERVED | MI        | Modem Interconnect          | 52  | CTRLSIN_P    | MI       | Modem Interconnect          |

| 3   | EYESYNC         | OA        | Eye Pattern Circuit         | 53  | RESERVED     | MI       | Modem Interconnect          |

| 4   | EYECLK          | OA        | Eye Pattern Circuit         | 54  | SOUT_P       | MI       | Modem Interconnect          |

| 5   | RXD             | OA        | DTE serial interface        | 55  | SIN_P        | MI       | Modem Interconnect          |

| 6   | SR1IO           | MI        | Modem Interconnect          | 56  | FSYNC_P      | MI       | Modem Interconnect          |

| 7   | NC              | -         | No Connection               | 57  | IARESET_P#   | MI       | Modem Interconnect          |

| 8   | EYEXY           | OA        | Eye Pattern Circuit         | 58  | AGND3        | GND      | IA Analog Ground            |

| 9   | SR4OUT          | MI        | Modem Interconnect          | 59  | NC           | -        | No Connection               |

| 10  | VDD1            | PWR       | 3.3V Digital Supply for DSP | 60  | LINEIN_P     | I        | Line Interface              |

| 11  | RLSD#           | OB        | DTE Serial Interface        | 61  | MICP_P       | I        | Microphone Input            |

| 12  | DCLK            | OB        | DTE Serial Interface        | 62  | MICM_P       | I        | Microphone Input            |

| 13  | EN85#           | IA        | Host Parallel Interface     | 63  | MICBIAS_P    | 0        | Microphone Bias Output      |

| 14  | GPI0            | IA        | Host Parallel Interface     | 64  | NC           | -        | No Connection               |

| 15  | RTS#            | IA        | DTE Serial Interface        | 65  | NC           | NC       | No Connection               |

| 16  | DGND1           | GND       | DSP Digital Ground          | 66  | VREF_P       | MI       | Modem Interconnect          |

| 17  | TXD             | IA        | DTE Serial Interface        | 67  | VC_P         | MI       | Modem Interconnect          |

| 18  | SA1CLK          | MI        | Modem Interconnect          | 68  | VAA_P        | PWR      | 5V Analog Supply for IA     |

| 19  | RS4             | IB        | Host Parallel Interface     | 69  | LINEOUT_P    | 0        | Line Interface              |

| 20  | RS3             | IB        | Host Parallel Interface     | 70  | AGND4        | GND      | IA Analog Ground            |

| 21  | RS2             | IB        | Host Parallel Interface     | 71  | SPKRP_P      | 0        | Speaker Interface Output    |

| 22  | RS1             | IB        | Host Parallel Interface     | 72  | SPKRM_P      | 0        | Speaker Interface Output    |

| 23  | RS0             | IB        | Host Parallel Interface     | 73  | AVDD_P       | PWR      | 5V Digital power for IA     |

| 24  | YCLK            | I         |                             | 74  | NC           | -        | No Connection               |

| 25  | IACLK           | MI        | Modem Interconnect          | 75  | ICLK_P       | MI       | Modem Interconnect          |

| 26  | IA1CLK          | MI        | Modem Interconnect          | 76  | MCLK_S/NC    | MI       | Modem Interconnect          |

| 27  | CTRLSIN_S/NC    | MI        | Modem Interconnect          | 77  | VDD2         | PWR      | 3.3V Digital Supply for DSP |

| 28  | RESERVED/NC     | MI        | Modem Interconnect          | 78  | D7           | IB/OC    | Host Parallel Interface     |

| 29  | SOUT_S/NC       | MI        | Modem Interconnect          | 79  | D6           | IB/OC    | Host Parallel Interface     |

| 30  | SIN_S/NC        | MI        | Modem Interconnect          | 80  | D5           | IB/OC    | Host Parallel Interface     |

| 31  | FSYNC_S/NC      | MI        | Modem Interconnect          | 81  | D4           | IB/OC    | Host Parallel Interface     |

| 32  | IARESET_S#/NC   | MI        | Modem Interconnect          | 82  | D3           | IB/OC    | Host Parallel Interface     |

| 33  | AGND1           | GND       | IA Analog Ground            | 83  | D2           | IB/OC    | Host Parallel Interface     |

| 34  | LINEIN_S/NC     | 1         | Line Interface              | 84  | DGND2        | GND      | DSP Digital Ground          |

| 35  | MICP_S/NC       | I         | Microphone Input            | 85  | VDD3         | PWR      | 3.3V Digital Supply for DSP |

| 36  | MICM_S/NC       | 1         | Microphone Input            | 86  | D1           | IB/OC    | Host Parallel Interface     |

| 37  | MICBIAS_S/NC    | 0         | Microphone Bias Output      | 87  | DGND3        | GND      | DSP Digital Ground          |

| 38  | NC              | -         | No Connection               | 88  | D0           | IB/OC    | Host Parallel Interface     |

| 39  | NC              | -         | No Connection               | 89  | CSBR#        | IB       | Host Parallel Interface     |

| 40  | VREF_S/NC       | MI        | Modem Interconnect          | 90  | WRITE#       | IB       | Host Parallel Interface     |

| 41  | VC_S/NC         | MI        | Modem Interconnect          | 91  | CS#          | IB       | Host Parallel Interface     |

| 42  | VAA_S/NC        | PWR       | 5V IA Analog power          | 92  | READ#        | IB       | Host Parallel Interface     |

| 43  | LINEOUT_S/NC    | 0         | Line Interface              | 93  | GPI2         | IA       | General purpose input       |

| 44  | NC NC           | -         | No Connection               | 94  | GPI3         | IA       | General purpose input       |

| 45  | AGND2           | GND       | IA Analog Ground            | 95  | GPI4         | IA       | General purpose input       |

| 46  | SPKRP S/NC      | 0         | Speaker Interface Output    | 96  | GPI5         | IA       | General purpose input       |

| 47  | SPKRM_S/NC      | 0         | Speaker Interface Output    | 97  | GPI6         | IA       | General purpose input       |

| 48  | AVDD S/NC       | PWR       | 5V IA Digital power         | 98  | GPI7         | IA       | General purpose input       |

| 49  | RESERVED/NC     | MI        | Modem Interconnect          | 99  | GP07         | OC       | General purpose output      |

| 50  | ICLK S/NC       | MI        | Modern Interconnect         | 100 | VDD4         | PWR      | 3.3V DSP Digital Power      |

| υU  | ICLN_S/NC       | IVII      | wodem interconnect          | 100 | V D D 4      | PVVK     | 3.3V DSP Digital Power      |

Table 2-1. FM209/214 Modem Pin Signals - 128-Pin TQFP (Cont'd)

| Pin | Signal Label | I/O Type | Interface              | Pin | Signal Label | I/O Type | Interface             |

|-----|--------------|----------|------------------------|-----|--------------|----------|-----------------------|

| 101 | GPO6         | OC       | General purpose output | 115 | RESET#       | IB       | External reset        |

| 102 | GPO5         | OC       | General purpose output | 116 | XTALI        | ı        | Crystal in            |

| 103 | RESERVED     | MI       | Modem Interconnect     | 117 | XTALO        | 0        | Crystal Out           |

| 104 | GPO4         | OC       | General purpose output | 118 | RESERVED     | MI       | Modem Interconnect    |

| 105 | GPO3         | OC       | General purpose output | 119 | XCLK         | OB       | X clock output        |

| 106 | DGND4        | GND      | DSP Digital Ground     | 120 | GPI1         | IA       | General purpose input |

| 107 | CTS#         | OB       | DTE Serial Interface   | 121 | IRQ2#        | OA       | Interrupt request     |

| 108 | IRQ1#        | OB       | Interrupt request      | 122 | SR3IN        | MI       | Modem Interconnect    |

| 109 | GPO2         | OC       | General purpose output | 123 | RESERVED     | MI       | Modem Interconnect    |

| 110 | GPO1         | OC       | General purpose output | 124 | RESERVED     | MI       | Modem Interconnect    |

| 111 | GPO0         | OC       | GPO0 (IAreset)         | 125 | DGND6        | GND      | DSP Digital Ground    |

| 112 | VDD5         | PWR      | 3.3V DSP Digital Power | 126 | DVAA         | PWR      | 3.3V DSP analog power |

| 113 | VGG          | PWR      | 5V DSP Digital         | 127 | AGND5        | GND      | DSP Analog Ground     |

| 114 | DGND5        | GND      | DSP Digital Ground     | 128 | RESERVED     | MI       | Modem Interconnect    |

#### Notes:

I/O types:

MI = Modem interconnect.

IA, IB, = digital input (see Table 2-3).

OA, OB, OC = digital output (see Table 2-3).

I = analog input (see Table 2-4).

O = analog output (see Table 2-4).

\_P Signals: Primary IA

\_S Signals: Secondary IA

Reserved = No external connection allowed.

**Table 2-2. Modem Hardware Interface Signal Definitions**

| Label        | I/O Type | Type Interface Signal Definition                                                                                                                                                                                                                                                                                 |  |  |  |  |

|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|              |          | OVERHEAD SIGNALS                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| XTLI, XTLO   | I/O      | Crystal In and Crystal Out. The modem must be connected to an external crystal circuit consisting of a 32.256 MHz crystal.                                                                                                                                                                                       |  |  |  |  |

| RESET#       | IB       | Reset. After application of +5V power to the modem, RESET# must be held low for at least 15 ms after the +5V power reaches operating range. The modem is ready to use 25 ms after the low-to-high transition of RESET#. The reset sequence initializes the modem interface memory (Table 3-1) to default values. |  |  |  |  |

| VGG          | PWR      | 5V Supply Voltage for DSP Digital Circuits.                                                                                                                                                                                                                                                                      |  |  |  |  |

| AVDD_P,      | PWR      | 3.3V Supply Voltage for IA Digital Circuits. Connect to VCC through decoupling circuit.                                                                                                                                                                                                                          |  |  |  |  |

| AVDD_S       |          |                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| VAA_P, VAA_S | PWR      | 5V Supply Voltage for IA Analog Circuits. Connect to VCC through decoupling circuit.                                                                                                                                                                                                                             |  |  |  |  |

| VDDn         | PWR      | 3.3V Supply Voltage for DSP Digital Circuits.                                                                                                                                                                                                                                                                    |  |  |  |  |

| DVAA         | PWR      | 3.3V Supply Voltage for DSP Analog Circuits.                                                                                                                                                                                                                                                                     |  |  |  |  |

| DGNDn        | GND      | Ground for Digital Circuits. Connect to digital ground.                                                                                                                                                                                                                                                          |  |  |  |  |

| AGNDn        | GND      | Ground for Analog Circuits. Connect to analog ground.                                                                                                                                                                                                                                                            |  |  |  |  |

|              |          | MICROPROCESSOR BUS INTERFACE                                                                                                                                                                                                                                                                                     |  |  |  |  |

Address, data, control, and interrupt hardware interface signals allow modem connection to an 8085 or 6500 bus compatible microprocessor. With the addition of external logic, the interface can be made compatible with a wide variety of other microprocessors, such

as the 8080 or 68000.

The microprocessor interface allows a microprocessor to change modem configuration, read or write channel and diagnostic data, and

supervise modem operation by writing control bits and reading status bits.

**Note:** The modem should not be continuously selected for read operation. Also, read or write operations should be delayed by at least 2 XCLK cycles from a preceding write cycle.

| D0-D7   | IB/OC | <b>Data Lines.</b> Eight bi-directional data lines (D0–D7) provide parallel transfer of data between the host and the modem. The most significant bit is D7. Data direction is controlled by the Read Enable (READ#-Ø2) and Write Enable (WRITE#-R/W#) signals.                                                             |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       | During a read cycle, data from the DSP interface memory register is gated onto the data bus via three-state drivers in the DSP. These drivers force the data lines high for a one bit, or low for a zero bit. When not read, the three-state drivers assume their high-impedance (off) state.                               |

|         |       | During a write cycle, data from the data bus is copied into the selected DSP interface memory register, with high and low bus levels representing one and zero bit states, respectively.                                                                                                                                    |

| RS0-RS4 | IB    | <b>Register Select Lines.</b> Five active high Register Select inputs (RS0–RS4) address interface memory registers within the DSP when CS# is low. These lines are typically connected to address lines A0-A4.                                                                                                              |

|         |       | When selected by CS# low, the DSP decodes RS0 through RS4 to address one of 32 8-bit internal interface memory registers (00-1F). The most significant address bit is RS4 while the least significant address bit is RS0. The selected register can be read from, or written into, via the 8-bit parallel data bus (D0–D7). |

| CS#     | IB    | <b>Chip Select.</b> The active low CS# input selects and enables the modem DSP for parallel data transfer between the DSP and the host over the microprocessor bus.                                                                                                                                                         |

| CSBR#   | IB    | Chip Select Buffer RAM. Active low chip select used when CS# is active to select Interface Memory (CSBR# high) or Buffer RAM (CSBR# low).                                                                                                                                                                                   |

Table 2-2. Modem Hardware Interface Signal Definitions (Cont'd)

| Label           | I/O Type  |                                                                                                                                                                                                     | Interface Si                                                 | ignal Definitior                                                                                                            | 1                                     |                                                         |

|-----------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------------|

| READ#           | IB        | Read Enable. When EN85# is low                                                                                                                                                                      | `                                                            | ,                                                                                                                           | •                                     | host pulsing READ#                                      |

|                 |           | input low during the microprocessor                                                                                                                                                                 | r bus access cycle                                           | e. The read timi                                                                                                            | ing is:                               |                                                         |

|                 |           | Parameter                                                                                                                                                                                           | Symbol                                                       | Min.                                                                                                                        | Max.                                  | Units                                                   |

|                 |           | CS# Setup Time                                                                                                                                                                                      | TCS                                                          | 0                                                                                                                           | _                                     | ns                                                      |

|                 |           | RSi Setup Time                                                                                                                                                                                      | TRS                                                          | 10                                                                                                                          | -                                     | ns                                                      |

|                 |           | Data Access Time                                                                                                                                                                                    | TDA                                                          | _                                                                                                                           | 45                                    | ns                                                      |

|                 |           | Data Hold Time                                                                                                                                                                                      | TDHR                                                         | 10                                                                                                                          | _                                     | ns                                                      |

|                 |           | Control Hold Time                                                                                                                                                                                   | THC                                                          | 10                                                                                                                          | _                                     | ns                                                      |

|                 |           | Notes:                                                                                                                                                                                              |                                                              |                                                                                                                             |                                       |                                                         |

|                 |           | CS# and READ# must not bot                                                                                                                                                                          | •                                                            |                                                                                                                             |                                       |                                                         |

|                 |           | A read or write operation follow                                                                                                                                                                    | ving a read opera                                            | tion must be de                                                                                                             | elayed by at leas                     | st 2 XCLK cycle.                                        |

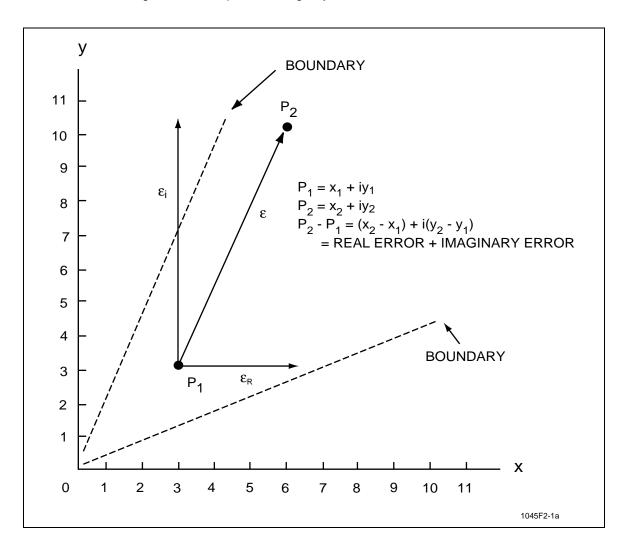

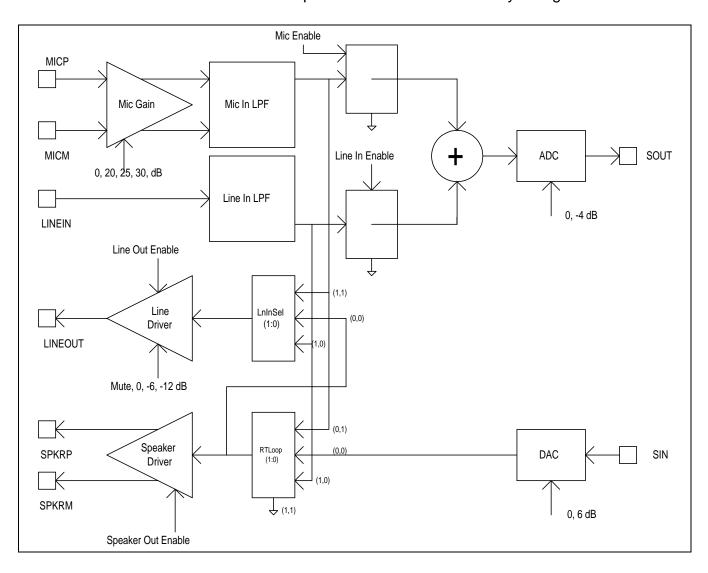

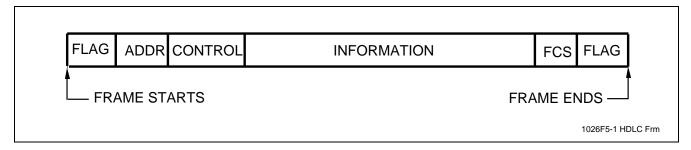

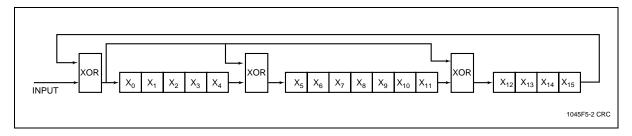

| WRITE#-R/W#     | IB        | Write Enable–R/W#. When EN85# WRITE# input low during the microp                                                                                                                                    | ,                                                            |                                                                                                                             | •                                     | by the host pulsing                                     |